- 您现在的位置:买卖IC网 > PDF目录17049 > EVAL-AD7764EDZ (Analog Devices Inc)BOARD EVAL AD7764 PDF资料下载

参数资料

| 型号: | EVAL-AD7764EDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/33页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL AD7764 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 312k |

| 数据接口: | 串行 |

| 输入范围: | ±3.2768 V |

| 在以下条件下的电源(标准): | 300mW @ 312kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7764 |

| 已供物品: | 板,CD |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

AD7764

Rev. A | Page 21 of 32

AD7764 INTERFACE

READING DATA

The AD7764 uses an SPI-compatible serial interface. The

timing diagram in Figure 2 shows how the AD7764 transmits its

con-version results.

The data read from the AD7764 is clocked out using the serial

clock output (SCO). The SCO frequency is half that of the

MCLK input to the AD7764.

The conversion result output on the serial data output (SDO)

line is framed by the frame synchronization output, FSO

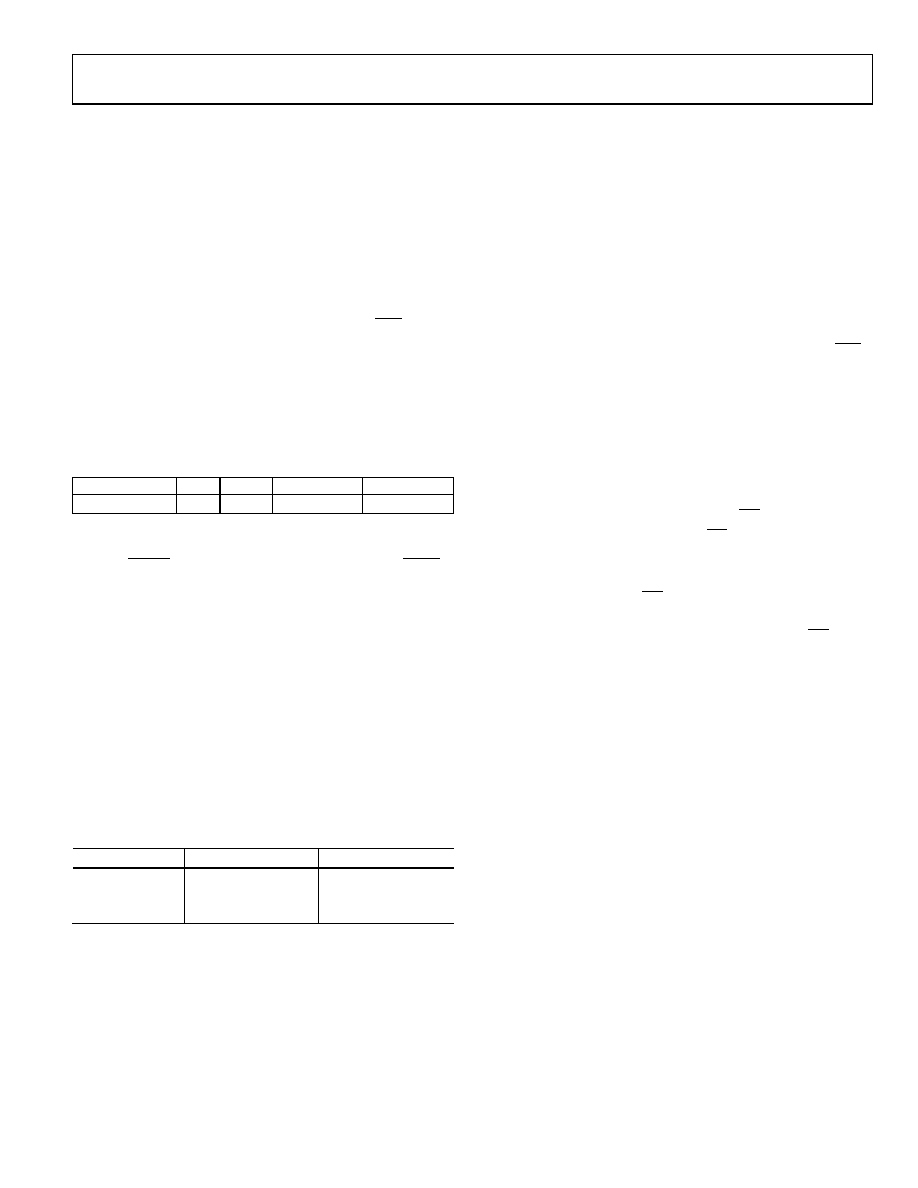

Table 9. Status Bits During Data Read

, which

is sent logic low for 32 SCO cycles. Each bit of the new conversion

result is clocked onto the SDO line on the rising SCO edge and

is valid on the falling SCO edge. The 32-bit result consists of the

24 data bits followed by five status bits followed further by three

zeros. The five status bits are listed in Table 9 and described

below the table.

D7

D6

D5

D4

D3

FILTER-SETTLE

OVR

LPWR

DEC_RATE 1

DEC_RATE 0

The FILTER-SETTLE bit indicates whether the data output

from the AD7764 is valid. After resetting the device (using

the RESET pin) or clearing the digital filter (using the

The OVR (overrange) bit is described in the

SYNC

pin), the FILTER-SETTLE bit goes logic low to indicate

that the full settling time of the filter has not yet passed and

that the data is not yet valid. The FILTER-SETTLE bit also

goes to zero when the input to the part has asserted the

overrange alerts.

Alerts section.

The LPWR bit is set to logic high when the AD7764 is

operating in low power mode. See the Power Modes

section for further details.

The DEC_RATE 1 and DEC_RATE 0 bits indicate the

decimation ratio used. Table 10 is a truth table for the

decimation rate bits.

Table 10. Decimation Rate Status Bits

Decimate

DEC_RATE 1

DEC_RATE 0

64×

0

1

128×

1

256×

0

1Don’t care. If the DEC_RATE 1 bit is set to 1, AD7764 is in decimate

128× mode.

READING STATUS AND OTHER REGISTERS

The AD7764 features a gain correction register, an overrange

register, and a read-only status register. To read back the

contents of these registers, the user must first write to the

control register of the device and set the bit that corresponds to

the register to be read. The next read operation outputs the

contents of the selected register (on the SDO pin) instead of a

conversion result.

To ensure that the next read cycle contains the contents of the

register written to, the write operation to that register must be

completed a minimum of 8 × tSCO before the falling edge of FSO

The

,

which indicates the start of the next read cycle. See Figure 4 for

further details.

AD7764 Registers section provides more information on

the relevant bits in the control register.

WRITING TO THE AD7764

A write operation to the AD7764 is shown in Figure 3. The

serial writing operation is synchronous to the SCO signal. The

status of the frame synchronization input, FSI, is checked on the

falling edge of the SCO signal. If the FSI line is low, then the

first data bit on the serial data in (SDI) line is latched in on the

next SCO falling edge.

Set the active edge of the FSI signal to occur at a position when

the SCO signal is high or low to allow setup and hold times

from the SCO falling edge to be met. The width of the

FSI

signal can be set to between 1 and 32 SCO periods wide. A

second, or subsequent, falling edge that occurs before 32 SCO

periods have elapsed is ignored.

details the format for the serial data being written to

the AD7764 through the SDI pin. Thirty-two bits are required

for a write operation. The first 16 bits are used to select the

register address that the data being read is intended for. The

second 16 bits contain the data for the selected register.

Writing to the AD7764 is allowed at any time, even while

reading a conversion result. Note that, after writing to the

devices, valid data is not output until after the settling time

for the filter has elapsed. The FILTER-SETTLE status bit is

asserted at this point to indicate that the filter has settled and

that valid data is available at the output.

相关PDF资料 |

PDF描述 |

|---|---|

| STD01W-U | WIRE & CABLE MARKERS |

| DK-DEV-1AGX60N | KIT DEV ARRIA GX 1AGX60N |

| GBM25DRSS | CONN EDGECARD 50POS DIP .156 SLD |

| STD01W-C | WIRE & CABLE MARKERS |

| EVAL-AD7170EBZ | BOARD EVAL FOR AD7170 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7765EBZ | 制造商:Analog Devices 功能描述:EVAL BOARD 24BIT, 312KSPS, 109DB - Bulk |

| EVAL-AD7765EDZ | 功能描述:BOARD EVAL AD7765 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7766-1EDZ | 功能描述:BOARD EVAL AD7766-1 64KSPS 111DB RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7766-2EDZ | 功能描述:BOARD EVAL AD7766-2 32KSPS 114DB RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7766EDZ | 功能描述:BOARD EVAL AD7766 128KSPS 108DB RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。