- 您现在的位置:买卖IC网 > PDF目录16522 > EVAL-ADAU1381Z (Analog Devices Inc)BOARD EVALUATION FOR ADAU1381 PDF资料下载

参数资料

| 型号: | EVAL-ADAU1381Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 18/84页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR ADAU1381 |

| 标准包装: | 1 |

| 主要目的: | 音频编解码器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ADAU1381 |

| 已供物品: | 板 |

| 相关产品: | ADAU1381BCBZ-RL7DKR-ND - IC AUDIO CODEC STEREO LN 30WLCSP ADAU1381BCBZ-RL7CT-ND - IC AUDIO CODEC STEREO LN 30WLCSP ADAU1381BCBZ-RL-ND - IC AUDIO CODEC STEREO LN 30WLCSP ADAU1381BCPZ-RL7-ND - IC AUDIO CODEC STEREO LN 32LFCSP ADAU1381BCPZ-RL-ND - IC AUDIO CODEC STEREO LN 32LFCSP ADAU1381BCBZ-RL7TR-ND - IC AUDIO CODEC STEREO LN 30WLCSP ADAU1381BCPZ-ND - IC AUDIO CODEC STEREO LN 32LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

ADAU1381

Rev. B | Page 25 of 84

STARTUP, INITIALIZATION, AND POWER

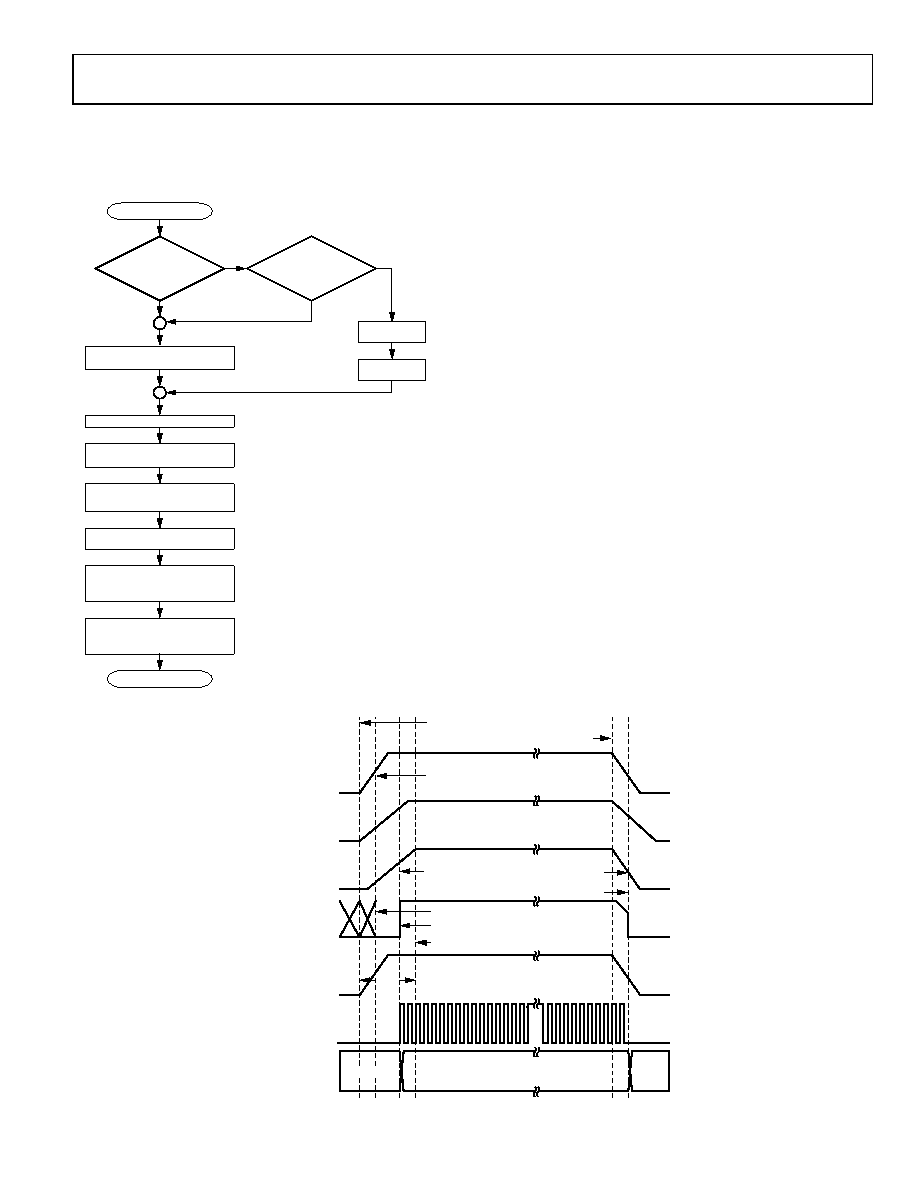

This section details the procedure for setting up the ADAU1381

properly. Figure 27 provides an overview of how to initialize the IC.

START

CONFIGURE CLOCK GENERATION

REGISTER 16384 (0x4000)

AND REGISTER 16386 (0x4002)

SUPPLY POWER TO AVDD1/AVDD2

PINS SIMULTANEOUSLY

SET UP SOUND ENGINE REGISTERS

FOR CUSTOMIZED SIGNAL PATH

(INCLUDING VOLUME, SAMPLE RATES,

FILTER COEFFICIENTS)

INITIALIZATION

COMPLETE

WAIT 14ms FOR POWER-ON RESET

AND INITIALIZATION ROM BOOT

SUPPLY POWER TO IOVDD

ENABLE DIGITAL POWER TO

FUNCTIONAL SUBSYSTEMS

REGISTER 16512 (0x4080)

AND REGISTER 16513 (0x4081)

WAIT FOR PLL LOCK

(2.4ms TO 3.5ms)

ARE AVDD1 AND AVDD2

SUPPLIED SEPARATELY?

CAN AVDD1 AND AVDD2

BE SIMULTANEOUSLY

SUPPLIED?

SUPPLY POWER

TO AVDD2

SUPPLY POWER

TO AVDD1

NO

YES

08

31

3-

02

5

NO

Figure 27. Initialization Sequence

POWER-UP SEQUENCE

If AVDD1 and AVDD2 are from the same supply, they can

power up simultaneously. If AVDD1 and AVDD2 are from

separate supplies, then AVDD1 should be powered up first.

IOVDD should be applied simultaneously with AVDD1, if

possible.

The ADAU1381 uses a power-on reset (POR) circuit to reset the

registers upon power-up. The POR monitors the DVDDOUT

pin and generates a reset signal whenever power is applied to

the chip. During the reset, the ADAU1381 is set to the default

values documented in the register map (see the Control Register

Map section).

The POR is also used to prevent clicks and pops on the speaker

driver output. The power-up sequencing and timing involved is

Figure 37 of the Speaker Output section.

A self-boot ROM initializes the memories after the POR has

completed. When the self-boot sequence is complete, the control

registers are accessible via the I2C/SPI control port and should

then be configured as required for the application. Typically,

with a 10 μF capacitor on AVDD1, the power supply ramp-up,

POR, and self-boot combined take approximately 14 ms.

AVDD1

AVDD2

DVDDOUT

POWER-UP

(INTERNAL

SIGNAL)

INTERNAL MCLK

(NOT TO SCALE)

IOVDD

INPUT/OUTPUT

PINS

ACTIVE

1.35V

1.5V

0.95V

MAIN SUPPLY ENABLED

POR

ACTIVE

1.5V

MAIN SUPPLY DISABLED

14ms

HIGH-Z

POR COMPLETE/SELF-BOOT INITIATES

SELF-BOOT COMPLETE/MEMORY

IS ACCESSIBLE

POR ACTIVATES

0

831

3-

02

6

Figure 28. Power-Up and Power-Down Sequence Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| XR16V2751IM-0B-EB | EVAL BOARD FOR V2751 48TQFP |

| LBR2518T100M | INDUCTOR WOUND 10UH 235MA 1007 |

| VE-JVX-EZ-S | CONVERTER MOD DC/DC 5.2V 25W |

| A3CCH-2418G | IDC CABLE - AKC24H/AE24G/AKC24H |

| BA6238A | IC DRIVER REV MOTOR 2CH HSIP10 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADAU1401AEBZ | 功能描述:BOARD EVAL FOR ADAU1401A RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| EVAL-ADAU1401EB | 制造商:AD 制造商全称:Analog Devices 功能描述:SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| EVAL-ADAU1401EBZ | 功能描述:BOARD EVAL FOR ADAU1401 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:SigmaDSP® 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| EVAL-ADAU1401-EBZ | 制造商:Analog Devices 功能描述:EVALUATION KIT ((NS)) |

| EVAL-ADAU1442EBZ | 功能描述:BOARD EVAL FOR ADAU1442 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:SigmaDSP® 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

发布紧急采购,3分钟左右您将得到回复。