参数资料

| 型号: | EX128-PTQG100I |

| 厂商: | Microsemi SoC |

| 文件页数: | 46/48页 |

| 文件大小: | 0K |

| 描述: | IC FPGA ANTIFUSE 6K 100-TQFP |

| 标准包装: | 90 |

| 系列: | EX |

| 逻辑元件/单元数: | 256 |

| 输入/输出数: | 70 |

| 门数: | 6000 |

| 电源电压: | 2.3 V ~ 2.7 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页

eX Family FPGAs

Revision 10

1-3

Routing Resources

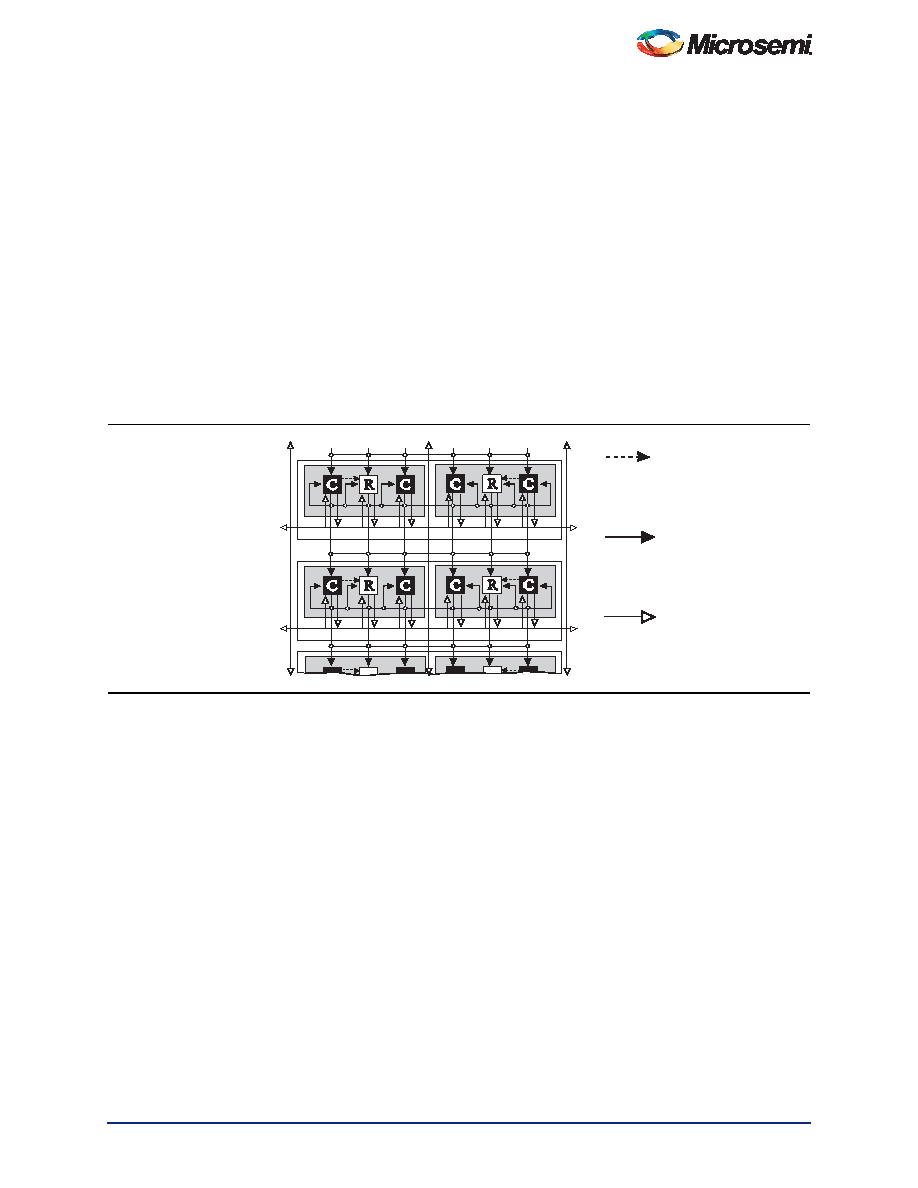

Clusters and SuperClusters can be connected through the use of two innovative local routing resources

called FastConnect and DirectConnect, which enable extremely fast and predictable interconnection of

modules within Clusters and SuperClusters (Figure 1-4). This routing architecture also dramatically

reduces the number of antifuses required to complete a circuit, ensuring the highest possible

performance.

DirectConnect is a horizontal routing resource that provides connections from a C-cell to its neighboring

R-cell in a given SuperCluster. DirectConnect uses a hard-wired signal path requiring no programmable

interconnection to achieve its fast signal propagation time of less than 0.1 ns (–P speed grade).

FastConnect enables horizontal routing between any two logic modules within a given SuperCluster and

vertical routing with the SuperCluster immediately below it. Only one programmable connection is used

in a FastConnect path, delivering maximum pin-to-pin propagation of 0.3 ns (–P speed grade).

In addition to DirectConnect and FastConnect, the architecture makes use of two globally oriented

routing resources known as segmented routing and high-drive routing. The segmented routing structure

of Microsemi provides a variety of track lengths for extremely fast routing between SuperClusters. The

exact combination of track lengths and antifuses within each path is chosen by the fully automatic place-

and-route software to minimize signal propagation delays.

Clock Resources

eX’s high-drive routing structure provides three clock networks. The first clock, called HCLK, is hardwired

from the HCLK buffer to the clock select MUX in each R-Cell. HCLK cannot be connected to

combinational logic. This provides a fast propagation path for the clock signal, enabling the 3.9 ns clock-

to-out (pad-to-pad) performance of the eX devices. The hard-wired clock is tuned to provide a clock skew

of less than 0.1 ns worst case. If not used, the HCLK pin must be tied LOW or HIGH and must not be left

floating. Figure 1-5 describes the clock circuit used for the constant load HCLK.

HCLK does not function until the fourth clock cycle each time the device is powered up to prevent false

output levels due to any possible slow power-on-reset signal and fast start-up clock circuit. To activate

HCLK from the first cycle, the TRST pin must be reserved in the Design software and the pin must be tied

to GND on the board. (See the "TRST, I/O Boundary Scan Reset Pin" on page 1-32).

The remaining two clocks (CLKA, CLKB) are global routed clock networks that can be sourced from

external pins or from internal logic signals (via the CLKINT routed clock buffer) within the eX device.

CLKA and CLKB may be connected to sequential cells or to combinational logic. If CLKA or CLKB is

sourced from internal logic signals, the external clock pin cannot be used for any other input and must be

tied LOW or HIGH and must not float. Figure 1-6 describes the CLKA and CLKB circuit used in eX

devices.

Figure 1-4 DirectConnect and FastConnect for SuperClusters

SuperClusters

DirectConnect

No antifuses

0.1 ns routing delay

FastConnect

One antifuse

0.5 ns routing delay

Routing Segments

Typically 2 antifuses

Max. 5 antifuses

相关PDF资料 |

PDF描述 |

|---|---|

| M1A3P400-1FG484 | IC FPGA 1KB FLASH 400K 484-FBGA |

| A40MX04-PLG44I | IC FPGA MX SGL CHIP 6K 44-PLCC |

| A40MX04-1PLG44 | IC FPGA MX SGL CHIP 6K 44-PLCC |

| A40MX04-1PL44 | IC FPGA MX SGL CHIP 6K 44-PLCC |

| A40MX02-2PLG44I | IC FPGA MX SGL CHIP 3K 44-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EX128-PTQG100PP | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:eX Family FPGAs |

| EX128-PTQG64 | 功能描述:IC FPGA ANTIFUSE 6K 64-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:EX 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| EX128-PTQG64I | 功能描述:IC FPGA ANTIFUSE 6K 64-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:EX 标准包装:90 系列:ProASIC3 LAB/CLB数:- 逻辑元件/单元数:- RAM 位总计:36864 输入/输出数:157 门数:250000 电源电压:1.425 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 125°C 封装/外壳:256-LBGA 供应商设备封装:256-FPBGA(17x17) |

| EX128-TQ100 | 功能描述:IC FPGA ANTIFUSE 6K 100-TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:EX 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

| EX128-TQ100A | 功能描述:IC FPGA ANTIFUSE 6K 100-TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:EX 标准包装:152 系列:IGLOO PLUS LAB/CLB数:- 逻辑元件/单元数:792 RAM 位总计:- 输入/输出数:120 门数:30000 电源电压:1.14 V ~ 1.575 V 安装类型:表面贴装 工作温度:-40°C ~ 85°C 封装/外壳:289-TFBGA,CSBGA 供应商设备封装:289-CSP(14x14) |

发布紧急采购,3分钟左右您将得到回复。