- 您现在的位置:买卖IC网 > PDF目录223866 > GS8662T06BD-350T (GSI TECHNOLOGY) 8M X 8 DDR SRAM, 0.45 ns, PBGA165 PDF资料下载

参数资料

| 型号: | GS8662T06BD-350T |

| 厂商: | GSI TECHNOLOGY |

| 元件分类: | SRAM |

| 英文描述: | 8M X 8 DDR SRAM, 0.45 ns, PBGA165 |

| 封装: | 13 X 15 MM, 1 MM PITCH, FPBGA-165 |

| 文件页数: | 14/33页 |

| 文件大小: | 651K |

| 代理商: | GS8662T06BD-350T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

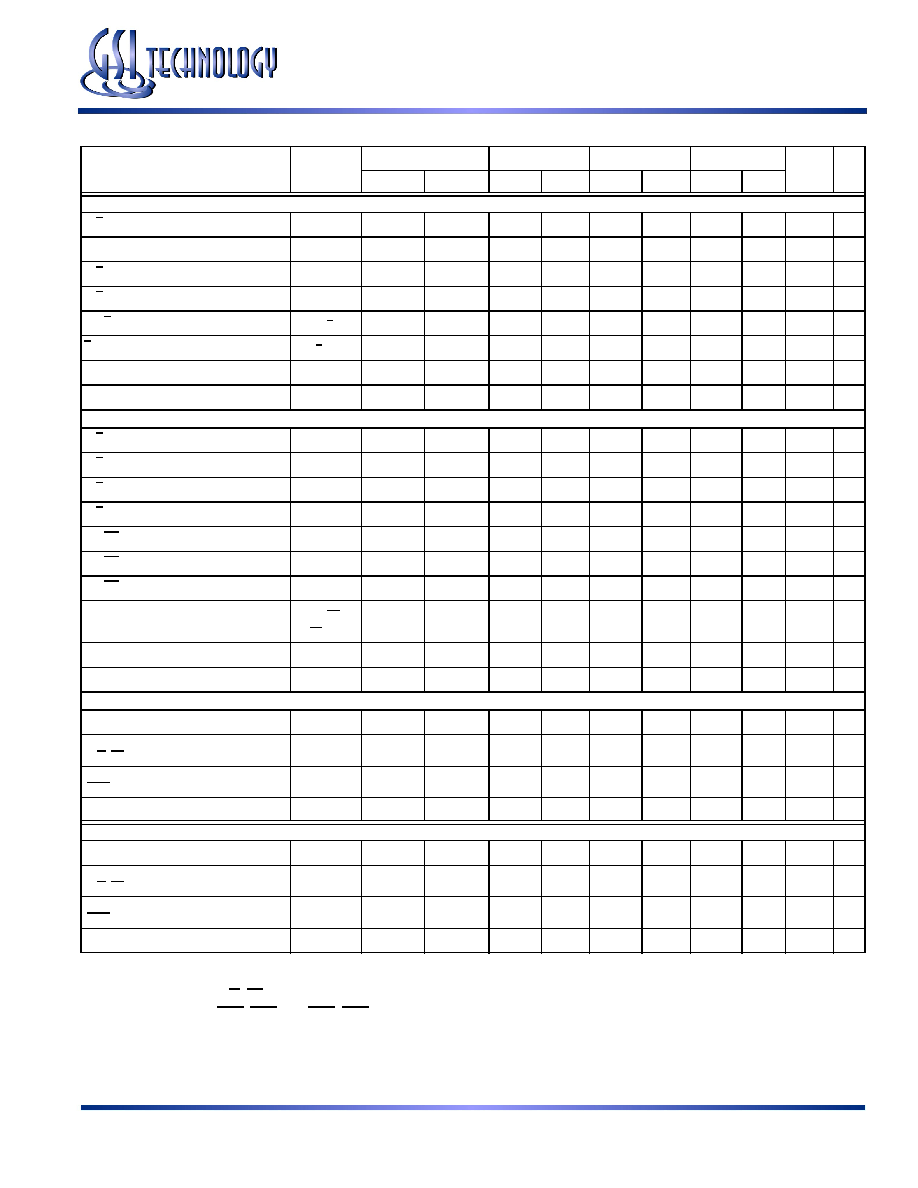

AC Electrical Characteristics (x8/x9)

Parameter

Symbol

-500

-450

-400

-350

Units

Notes

Min

Max

Min

Max

Min

Max

Min

Max

Clock

K, K Clock Cycle Time

tKHKH

2.0

8.4

2.2

8.4

2.5

8.4

2.86

8.4

ns

tK Variable

tKVar

—

0.15

—

0.15

—

0.2

—

0.2

ns

4

K, K Clock High Pulse Width

tKHKL

0.4

—

0.4

—

0.4

—

0.4

—

cycle

K, K Clock Low Pulse Width

tKLKH

0.4

—

0.4

—

0.4

—

0.4

—

cycle

K to K High

tKHKH

0.85

—

0.94

—

1.06

—

1.13

—

ns

K to K High

tKHKH

0.85

—

0.94

—

1.06

—

1.13

—

ns

DLL Lock Time

tKLock

2048

—

2048

—

2048

—

2048

—

cycle

5

K Static to DLL reset

tKReset

30

—

30

—

30

—

30

—

ns

Output Times

K, K Clock High to Data Output Valid

tKHQV

—

0.45

—

0.45

—

0.45

—

0.45

ns

K, K Clock High to Data Output Hold

tKHQX

–0.45

—

–0.45

—

–0.45

—

–0.45

—

ns

K, K Clock High to Echo Clock Valid

tKHCQV

—

0.33

—

0.37

—

0.45

—

0.45

ns

K, K Clock High to Echo Clock Hold

tKHCQX

–0.33

—

–0.37

—

–0.45

—

–0.45

—

ns

CQ, CQ High Output Valid

tCQHQV

—

0.15

—

0.15

—

0.2

—

0.23

ns

CQ, CQ High Output Hold

tCQHQX

–0.15

—

–0.15

—

–0.2

—

–0.23

—

ns

CQ, CQ High to QLVD

tQVLD

–0.15

0.15

-0.15

0.15

-0.2

0.2

–0.23

0.23

CQ Phase Distortion

tCQHCQH

0.75

—

0.85

—

1.0

—

1.0

—

ns

K Clock High to Data Output High-Z

tKHQZ

—

0.45

—

0.45

—

0.45

—

0.45

ns

K Clock High to Data Output Low-Z

tKHQX1

–0.45

—

–0.45

—

–0.45

—

–0.45

—

ns

Setup Times

Address Input Setup Time

tAVKH

0.25

—

0.275

—

0.4

—

0.4

—

ns

1

Control Input Setup Time

(R/W, LD)

tIVKH

0.25

—

0.275

—

0.4

—

0.4

—

ns

2

Control Input Setup Time

(BWX)

tIVKH

0.20

—

0.22

—

0.28

—

0.28

—

ns

3

Data Input Setup Time

tDVKH

0.20

—

0.22

—

0.28

—

0.28

—

ns

Hold Times

Address Input Hold Time

tKHAX

0.25

—

0.275

—

0.4

—

0.4

—

ns

1

Control Input Hold Time

(R/W, LD)

tKHIX

0.25

—

0.275

—

0.4

—

0.4

—

ns

2

Control Input Hold Time

(BWX)

tKHIX

0.20

—

0.22

—

0.28

—

0.28

—

ns

3

Data Input Hold Time

tKHDX

0.20

—

0.22

—

0.28

—

0.28

—

ns

Notes:

1. All Address inputs must meet the specified setup and hold times for all latching clock edges.

2. Control signals are R/W, LD.

3. Control signals are BW0, BW1 and (BW2, BW3 for x36).

4. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

5. VDD slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention. DLL lock time begins once VDD and input clock are stable.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.02 3/2011

21/33

2011, GSI Technology

GS8662T20/38BD-550/500/450/400/350

GS8662T06/11BD-500/450/400/350

相关PDF资料 |

PDF描述 |

|---|---|

| GS8672Q38BE-500I | 2M X 36 QDR SRAM, 0.45 ns, PBGA165 |

| GS880F32AGT-5.5IT | 256K X 32 CACHE SRAM, 5.5 ns, PQFP100 |

| GS880F32BGT-7IT | 256K X 32 CACHE SRAM, 7 ns, PQFP100 |

| GSAA07C-Q01 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.1A, 50VDC, PANEL MOUNT |

| GSAC36C-6Q02 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.1A, 50VDC, PANEL MOUNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GS8662T06BD-450 | 制造商:GSI Technology 功能描述:GS8662T06BD-450 - Trays |

| GS8662T06BD-500 | 制造商:GSI Technology 功能描述:GS8662T06BD-500 - Trays |

| GS8662T06BD-550 | 制造商:GSI Technology 功能描述:GS8662T06BD-550 - Trays |

| GS8662T07BD-450 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

| GS8662T08BD-400 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

发布紧急采购,3分钟左右您将得到回复。