- 您现在的位置:买卖IC网 > PDF目录223876 > HCPL-268K-100 Hermetically Sealed. High Speed. High CMR. Logic Gate Optocouplers PDF资料下载

参数资料

| 型号: | HCPL-268K-100 |

| 英文描述: | Hermetically Sealed. High Speed. High CMR. Logic Gate Optocouplers |

| 中文描述: | 密封。高速。高CMR。逻辑门光电耦合器 |

| 文件页数: | 12/12页 |

| 文件大小: | 259K |

| 代理商: | HCPL-268K-100 |

9

Notes:

1. Each channel.

2. All devices are considered two-terminal devices; II-O is measured between all input leads or terminals shorted together and all

output leads or terminals shorted together.

3. Measured between each input pair shorted together and all output connections for that channel shorted together.

4. Measured between adjacent input pairs shorted together for each multichannel device.

5. tPHL propagation delay is measured from the 50% point on the leading edge of the input pulse to the 1.5 V point on the leading

edge of the output pulse. The tPLH propagation delay is measured from the 50% point on the trailing edge of the input pulse to the

1.5 V point on the trailing edge of the output pulse.

6. The HCPL-6630, HCPL-6631, and HCPL-663K dual channel parts function as two independent single channel units. Use the single

channel parameter limits for each channel.

7. CML is the maximum rate of rise of the common mode voltage that can be sustained with the output voltage in the logic low state

(VO < 0.8 V). CMH is the maximum rate of fall of the common mode voltage that can be sustained with the output voltage in the

logic high state (VO > 2.0 V).

8. This is a momentary withstand test, not an operating condition.

9. It is essential that a bypass capacitor (0.01 to 0.1

F, ceramic) be connected from V

CC to ground. Total lead length between both

ends of this external capacitor and the isolator connections should not exceed 20 mm.

10. No external pull up is required for a high logic state on the enable input.

11. The tELH enable propagation delay is measured from the 1.5 V point on the trailing edge of the enable input pulse to the 1.5 V

point on the trailing edge of the output pulse.

12. The tEHL enable propagation delay is measured from the 1.5 V point on the leading edge of the enable input pulse to the 1.5 V

point on the leading edge of the output pulse.

13. Standard parts receive 100% testing at 25

°C (Subgroups 1 and 9). SMD and 883B parts receive 100% testing at 25, 125, and

-55

°C (Subgroups 1 and 9, 2 and 10, 3 and 11, respectively).

14. Parameters are tested as part of device initial characterization and after design and process changes. Parameters are guaranteed

to limits specified for all lots not specifically tested.

15. Not required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.

16. Required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.

17. Not required for HCPL-5650, HCPL-5651 and 8102805 types.

18. Required for HCPL-5650, HCPL-5651 and 8102805 types only.

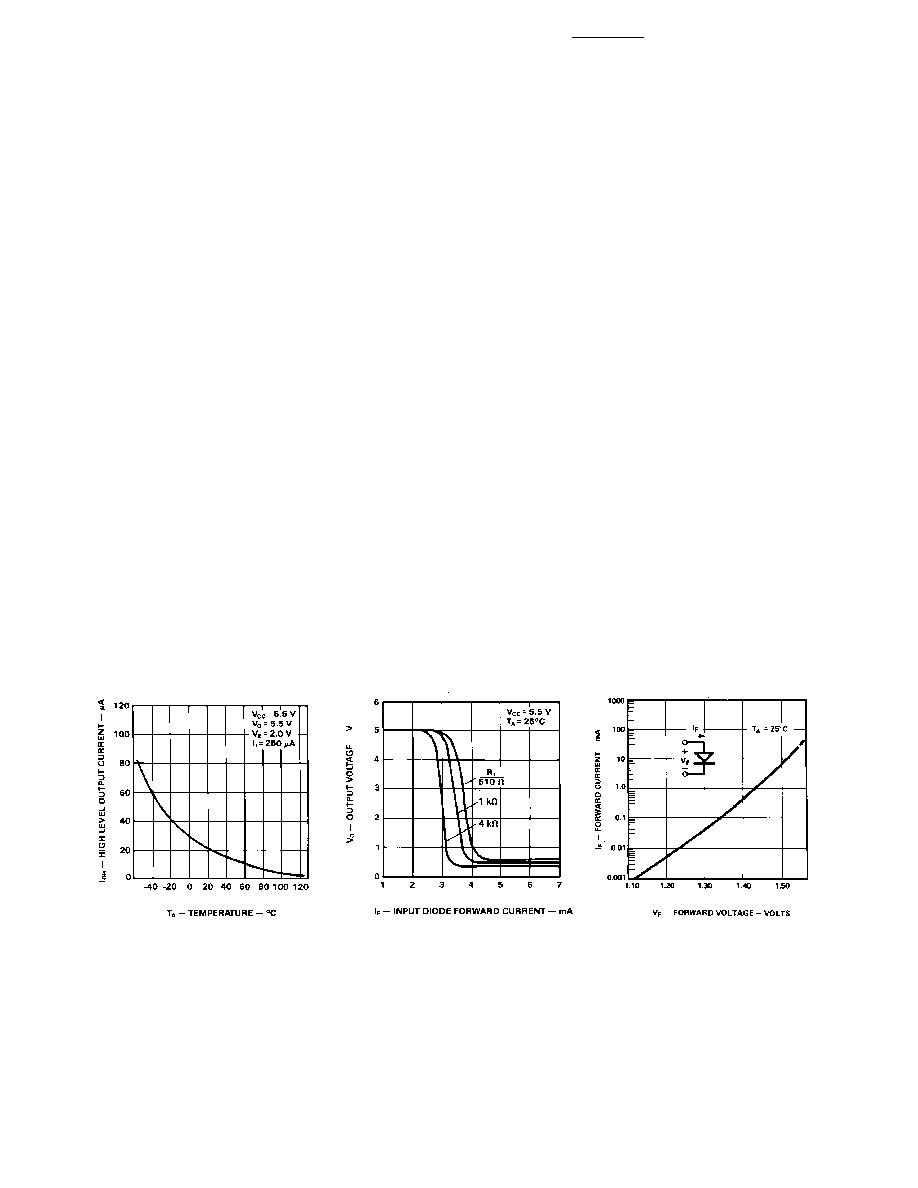

Figure 1. High Level Output Current

vs. Temperature.

Figure 2. Input-Output

Characteristics.

Figure 3. Input Diode Forward

Characteristic.

相关PDF资料 |

PDF描述 |

|---|---|

| HCPL-268K-300 | Hermetically Sealed. High Speed. High CMR. Logic Gate Optocouplers |

| HCPL-563K-100 | Receptacle With No Tail |

| HCPL-563K-300 | Receptacle With No Tail |

| HCPL-6630 | Hermetically Sealed. High Speed. High CMR. Logic Gate Optocouplers |

| HCPL-270L-500E | 1 CHANNEL LOGIC OUTPUT OPTOCOUPLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HCPL-268K-300 | 功能描述:高速光耦合器 10MBd 2Ch 1500Vdc Hermetically sealed RoHS:否 制造商:Avago Technologies 电流传递比: 最大波特率: 最大正向二极管电压:1.75 V 最大反向二极管电压:5 V 最大功率耗散:40 mW 最大工作温度:+125 C 最小工作温度:- 40 C 封装 / 箱体:SOIC-5 封装:Tube |

| HCPL270L | 制造商:AGILENT 制造商全称:AGILENT 功能描述:Low Input Current High Gain LVTTL/LVCMOS Compatible 3.3 V Optocouplers |

| HCPL-270L | 功能描述:高速光耦合器 100kBd 3.3V 0.5mA RoHS:否 制造商:Avago Technologies 电流传递比: 最大波特率: 最大正向二极管电压:1.75 V 最大反向二极管电压:5 V 最大功率耗散:40 mW 最大工作温度:+125 C 最小工作温度:- 40 C 封装 / 箱体:SOIC-5 封装:Tube |

| HCPL-270L#500 | 功能描述:高速光耦合器 100kBd 3.3V 0.5mA RoHS:否 制造商:Avago Technologies 电流传递比: 最大波特率: 最大正向二极管电压:1.75 V 最大反向二极管电压:5 V 最大功率耗散:40 mW 最大工作温度:+125 C 最小工作温度:- 40 C 封装 / 箱体:SOIC-5 封装:Tube |

| HCPL-270L-000E | 功能描述:高速光耦合器 100kBd 3.3V 0.5mA RoHS:否 制造商:Avago Technologies 电流传递比: 最大波特率: 最大正向二极管电压:1.75 V 最大反向二极管电压:5 V 最大功率耗散:40 mW 最大工作温度:+125 C 最小工作温度:- 40 C 封装 / 箱体:SOIC-5 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。