- 您现在的位置:买卖IC网 > PDF目录371784 > HCTL-2032 Quadrature Decoder/Counter Interface ICs PDF资料下载

参数资料

| 型号: | HCTL-2032 |

| 元件分类: | 通用总线功能 |

| 英文描述: | Quadrature Decoder/Counter Interface ICs |

| 中文描述: | 正交解码器/计数器接口芯片 |

| 文件页数: | 14/20页 |

| 文件大小: | 302K |

| 代理商: | HCTL-2032 |

14

Design Considerations

The designer should be aware

that the operation of the digital

filter places a timing constraint

on the relationship between

incoming quadrature signals and

the external clock. Figure 12

shows the timing waveform with

an incremental encoder input.

Since an input has to be stable

for three rising clock edges, the

encoder pulse width (t

E

- low

or high) has to be greater than

three clock periods (3t

CLK

). This

guarantees that the

asynchronous input will be

stable during three consecutive

rising clock edges. A realistic

design also has to take into

account finite rise time of the

waveforms, asymmetry of the

waveforms, and noise. In the

presence of large amounts of

noise, t

E

should be much

greater than 3t

CLK

to allow for

the interruption of the

consecutive level sampling by

the three-bit delay filter. It

should be noted that a change

on the inputs that is qualified

by the filter will internally

propagate in a maximum of

seven clock periods.

The quadrature decoder

circuitry imposes a second

timing constraint between the

external clock and the input

signals. There must be at least

one clock period between

consecutive quadrature states.

As shown in Figure 13, a

quadrature state is defined by

consecutive edges on both

channels. Therefore, t

ES

(encoder state period) > t

CLK

.

The designer must account for

deviations from the nominal 90

degree phasing of input signals

to guarantee that t

ES

> t

CLK

.

Position Counter

This section consists of a 32-bit

(HCTL-20XX-XX) binary up/

down counter which counts on

rising clock edges as explained

in the Quadrature Decoder

Section. All 32 bits of data are

passed to the position data

latch. The system can use this

count data in several ways:

A. System total range is 32 bits,

so the count represents

"absolute" position.

B. The system is cyclic with 32

bits of count per cycle. RST/ is

used to reset the counter every

cycle and the system uses the

data to interpolate within the

cycle.

C. System count is >8, 16, 24, or

32 bits, so the count data is

used as a relative or

incremental position input for a

system software computation of

absolute position. In this case

counter rollover occurs. In order

to prevent loss of position

information, the processor must

read the outputs of the IC

before the count increments

one-half of the maximum count

capability. Two's-complement

arithmetic is normally used to

compute position from these

periodic position updates.

D. The system count is >32 bits

so the HCTL-2032 / 2032-SC

can be cascaded with other

standard counter ICs to give

absolute position.

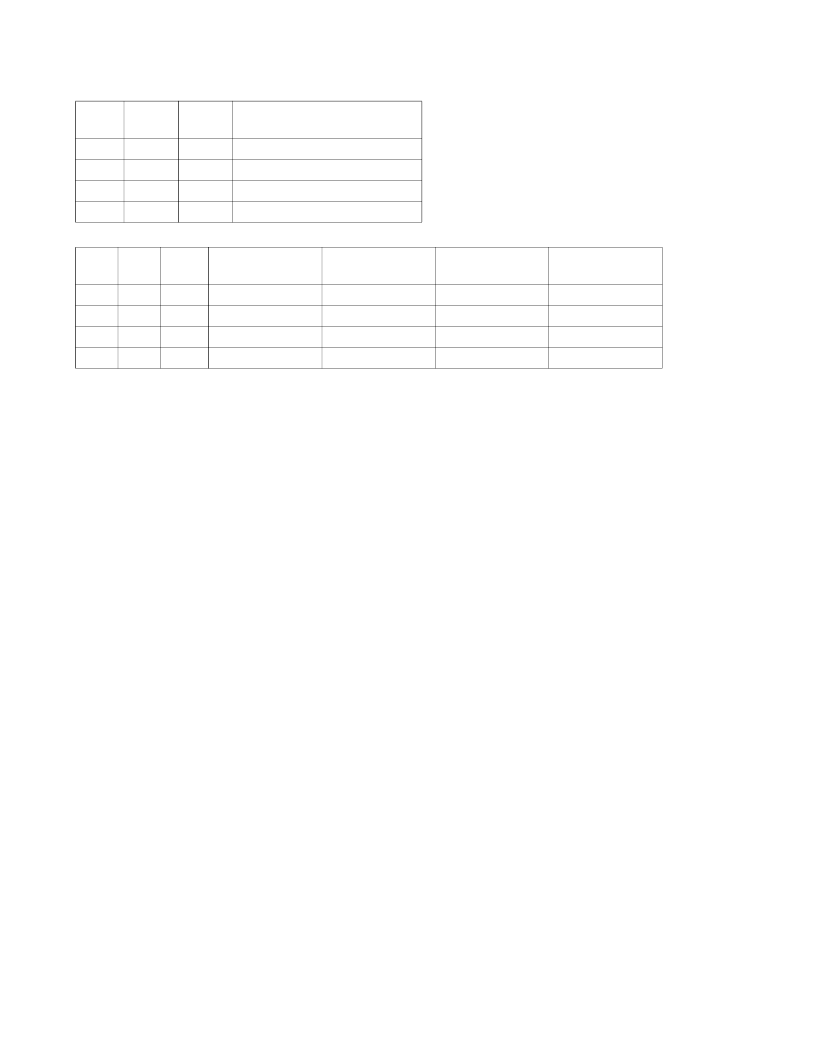

CHA

CHB

STATE

4X Decoder

(Count Up & Count Down)

Pulse

Pulse

Pulse

Pulse

1

1

0

0

0

1

1

0

1

2

3

4

Figure 13. 4x Decoder Mode

CHA

CHB

STATE

2x

Count Up

Pulse

-

Pulse

-

2x

Count Down

-

Pulse

-

Pulse

1x

Count Up

Pulse

-

-

-

1x

Count Down

-

Pulse

-

-

1

1

0

0

0

1

1

0

1

2

3

4

Figure 14. 2x and 1x Decoder Modes

相关PDF资料 |

PDF描述 |

|---|---|

| HCTL-2032-SC | Quadrature Decoder/Counter Interface ICs |

| HCTS00D | Radiation Hardened Quad 2-Input NAND Gate |

| HCTS00HMSR | Radiation Hardened Quad 2-Input NAND Gate |

| HCTS00DMSR | Radiation Hardened Quad 2-Input NAND Gate |

| HCTS00K | Radiation Hardened Quad 2-Input NAND Gate |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HCTL-2032-SC | 功能描述:接口 - 专用 Decoder/Counter RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| HCTL-2032-SCT | 制造商:Avago Technologies 功能描述:QUADRATURE DECODER/ COUNTER INTRFC IC 32PIN - Tape and Reel |

| HCT-L-R5A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Optoelectronic |

| HCT-L-R5B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Optoelectronic |

| HCT-L-R-HA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Optoelectronic |

发布紧急采购,3分钟左右您将得到回复。