- 您现在的位置:买卖IC网 > PDF目录385381 > HI5812KIB (HARRIS SEMICONDUCTOR) CMOS 20 Microsecond, 12-Bit, Sampling A/D Converter with Internal Track and Hold PDF资料下载

参数资料

| 型号: | HI5812KIB |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | ADC |

| 英文描述: | CMOS 20 Microsecond, 12-Bit, Sampling A/D Converter with Internal Track and Hold |

| 中文描述: | 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| 文件页数: | 10/13页 |

| 文件大小: | 427K |

| 代理商: | HI5812KIB |

6-1798

As long as these current spikes settle completely by end of

the signal acquisition period, converter accuracy will be

preserved. The analog input is tracked for 3 clock cycles.

With an external clock of 750kHz the track period is 4

μ

s.

A simplified analog input model is presented in Figure 19.

During tracking, the A/D input (V

IN

) typically appears as a

380pF capacitor being charged through a 420

internal

switch resistance. The time constant is 160ns. To charge this

capacitor from an external “zero

” source to 0.5 LSB

(1/8192), the charging time must be at least 9 time constants

or 1.4

μ

s. The maximum source impedance (R

SOURCE

Max)

for a 4

μ

s acquisition time settling to within 0.5LSB is 750

.

If the clock frequency was slower, or the converter was not

restarted immediately (causing a longer sample time), a

higher source impedance could be tolerated.

Reference Input

The reference input V

REF

+ should be driven from a low

impedance source and be well decoupled.

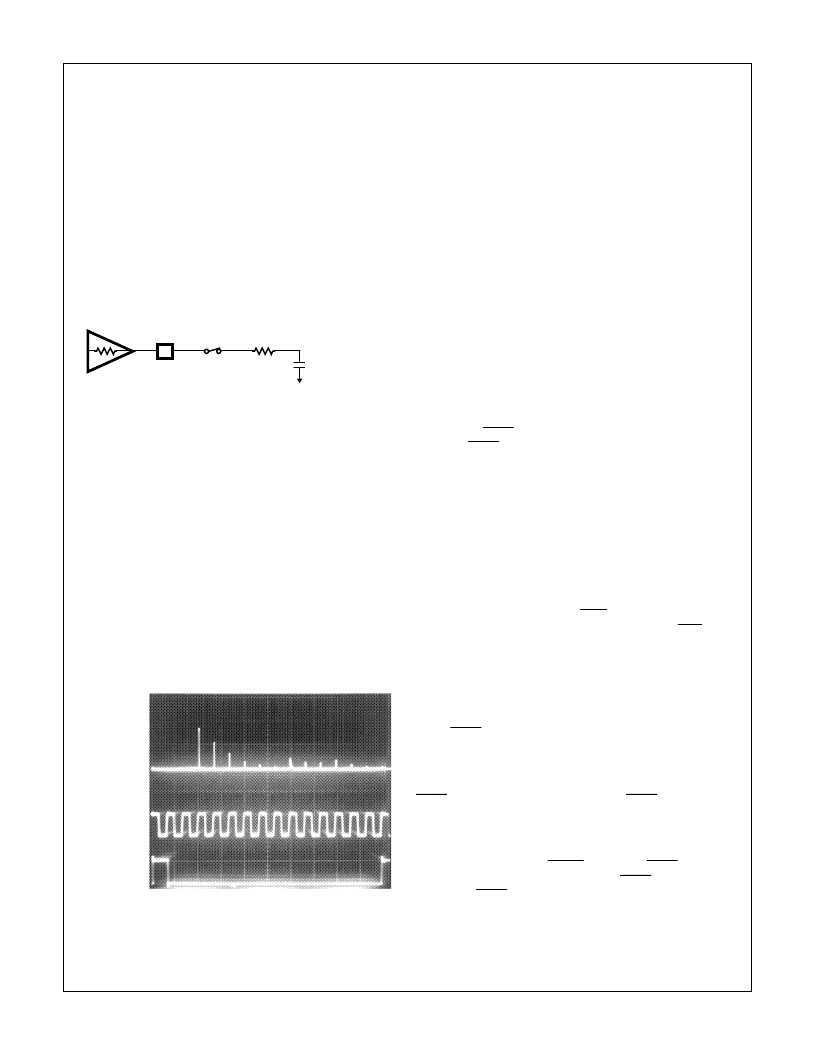

As shown in Figure 20, current spikes are generated on the

reference pin during each bit test of the successive approxi-

mation part of the conversion cycle as the charge-balancing

capacitors are switched between V

REF

- and V

REF

+ (clock

periods 5 - 14). These current spikes must settle completely

during each bit test of the conversion to not degrade the

accuracy of the converter. Therefore V

REF

+ and V

REF

-

should be well bypassed. Reference input V

REF

- is normally

connected directly to the analog ground plane. If V

REF

- is

biased for nulling the converters offset it must be stable

during the conversion cycle.

The HI5812 is specified with a 4.608V reference, however, it

will operate with a reference down to 3V having a slight

degradation in performance. A typical graph of accuracy vs

reference voltage is presented.

Full Scale and Offset Adjustment

In many applications the accuracy of the HI5812 would be

sufficient without any adjustments. In applications where

accuracy is of utmost importance full scale and offset errors

may be adjusted to zero.

The V

REF

+ and V

REF

- pins reference the two ends of the

analog input range and may be used for offset and full scale

adjustments. In a typical system the V

REF

- might be

returned to a clean ground, and the offset adjustment done

on an input amplifier. V

REF

+ would then be adjusted to null

out the full scale error. When this is not possible, the V

REF

-

input can be adjusted to null the offset error, however, V

REF

-

must be well decoupled.

Full scale and offset error can also be adjusted to zero in the

signal conditioning amplifier driving the analog input (V

IN

).

Control Signal

The HI5812 may be synchronized from an external source

by using the STRT (Start Conversion) input to initiate conver-

sion, or if STRT is tied low, may be allowed to free run. Each

conversion cycle takes 15 clock periods.

The input is tracked from clock period 1 through period 3,

then disconnected as the successive approximation takes

place. After the start of the next period 1 (specified by t

D

data), the output is updated.

The DRDY (Data Ready) status output goes high (specified

by t

D1

DRDY) after the start of clock period 1, and returns

low (specified by t

D2

DRDY) after the start of clock period 2.

The 12 data bits are available in parallel on three-state bus

driver outputs. When low, the OEM input enables the most

significant byte (D4 through D11) while the OEL input

enables the four least significant bits (D0 - D3). t

EN

and t

DIS

specify the output enable and disable times.

If the output data is to be latched externally, either the trailing

edge of data ready or the next falling edge of the clock after

data ready goes high can be used.

When STRT input is used to initiate conversions, operation is

slightly different depending on whether an internal or

external clock is used.

Figure 3 illustrates operation with an internal clock. If the

STRT signal is removed (at least t

R

STRT) before clock

period 1, and is not reapplied during that period, the clock

will shut off after entering period 2. The input will continue to

track and the DRDY output will remain high during this time.

A low signal applied to STRT (at least t

W

STRT wide) can

now initiate a new conversion. The STRT signal (after a

delay of (t

D

STRT)) causes the clock to restart.

Depending on how long the clock was shut off, the low

portion of clock period 2 may be longer than during the

remaining cycles.

R

SOURCE

V

IN

R

SW

≈

420

C

SAMPLE

≈

380pF

R

SOURCE(MAX)

t

–

C

SAMPLE

In 2

)

]

-------------------------------------------------------------

R

SW

–

=

FIGURE 19. ANALOG INPUT MODEL IN TRACK MODE

20mA

10mA

0mA

5V

0V

5V

0V

I

REF+

CLK

DRDY

2

μ

s/DIV.

CONDITIONS: V

DD

= V

AA

+ = 5.0V, V

REF

+ = 4.608V,

V

IN

= 2.3V, CLK = 750kHz, T

A

= 25

o

C

FIGURE 20. TYPICAL REFERENCE INPUT CURRENT

HI5812

相关PDF资料 |

PDF描述 |

|---|---|

| HI5812KIJ | CMOS 20 Microsecond, 12-Bit, Sampling A/D Converter with Internal Track and Hold |

| HI5812KIP | Silver Mica Capacitor; Capacitance:6200pF; Capacitance Tolerance:+/- 2%; Series:CD30; Voltage Rating:500VDC; Capacitor Dielectric Material:Mica; Termination:Radial Leaded; Lead Pitch:11.1mm; Leaded Process Compatible:Yes RoHS Compliant: Yes |

| HI5860 | 12-Bit, 130MSPS, High Speed D/A Converter(12位,130MHz,高速D/A转换器) |

| HI5905QML | 14 Bits 5MSPS Military A/D Converter(14位、5MSPS军用ADC) |

| HI5905 | 14-Bit, 5 MSPS A/D Converter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI5812KIBZ | 功能描述:ADC 12BIT 50KSPS 1LSB 24-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:12 采样率(每秒):3M 数据接口:- 转换器数目:- 功率耗散(最大):- 电压电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:SOT-23-6 供应商设备封装:SOT-23-6 包装:带卷 (TR) 输入数目和类型:- |

| HI5812KIJ | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS 20 Microsecond, 12-Bit, Sampling A/D Converter with Internal Track and Hold |

| HI5812KIP | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS 20 Microsecond, 12-Bit, Sampling A/D Converter with Internal Track and Hold |

| HI5812KIPS2267 | 制造商:Harris Corporation 功能描述: 制造商:Intersil Corporation 功能描述: |

| HI5813 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS 3.3V, 25 Microsecond, 12-Bit, Sampling A/D Converter with Internal Track and Hold |

发布紧急采购,3分钟左右您将得到回复。