- 您现在的位置:买卖IC网 > PDF目录17050 > HI5860SOICEVAL1 (Intersil)EVALUATION PLATFORM SOIC HI5860 PDF资料下载

参数资料

| 型号: | HI5860SOICEVAL1 |

| 厂商: | Intersil |

| 文件页数: | 4/8页 |

| 文件大小: | 0K |

| 描述: | EVALUATION PLATFORM SOIC HI5860 |

| 标准包装: | 1 |

| 系列: | CommLink™ |

| DAC 的数量: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 130M |

| 数据接口: | 并联 |

| 设置时间: | 35ns |

| DAC 型: | 电流 |

| 工作温度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | HI5860 |

�� �

�

�

�Application� Note� 9853�

�Appendix� A� Description� of� Architecture�

�The� segmented� current� source� architecture� has� the� ability� to�

�improve� the� converter’s� performance� by� reducing� the�

�amount� of� current� that� is� switching� at� any� one� time.� In�

�traditional� architectures,� major� transition� points� required� the�

�converter� to� switch� on� or� off� large� amounts� of� current.� In� a�

�traditional� 10-bit� R/2R� ladder� design,� for� example,� the�

�midscale� transition� required� approximately� equal� amounts� of�

�currents� switching� on� and� off.� In� a� segmented� current� source�

�arrangement,� transitions� such� as� midscale� become� one� in�

�which� you� simply� have� an� additional� intermediate� current�

�source� turning� on� and� several� minor� ones� turning� off.� In� the�

�case� of� the� HI5760,� there� are� 31� intermediate� current�

�segments� that� represent� the� 5� MSBs� and� ?ve,� binary-�

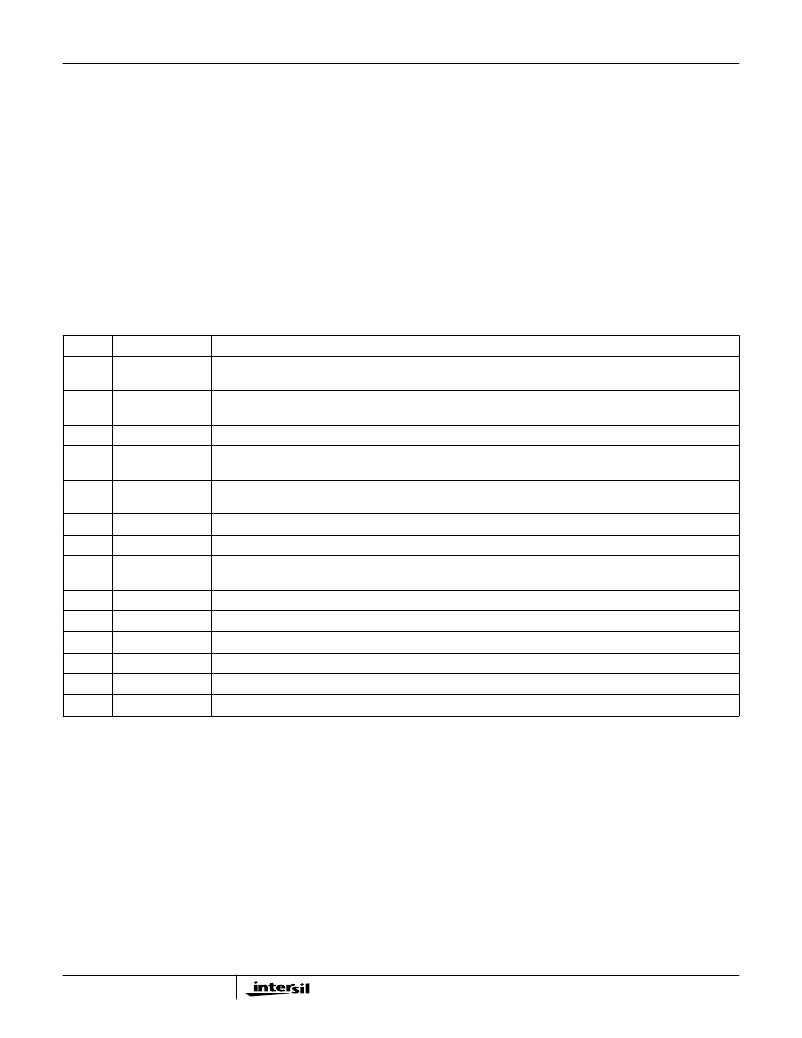

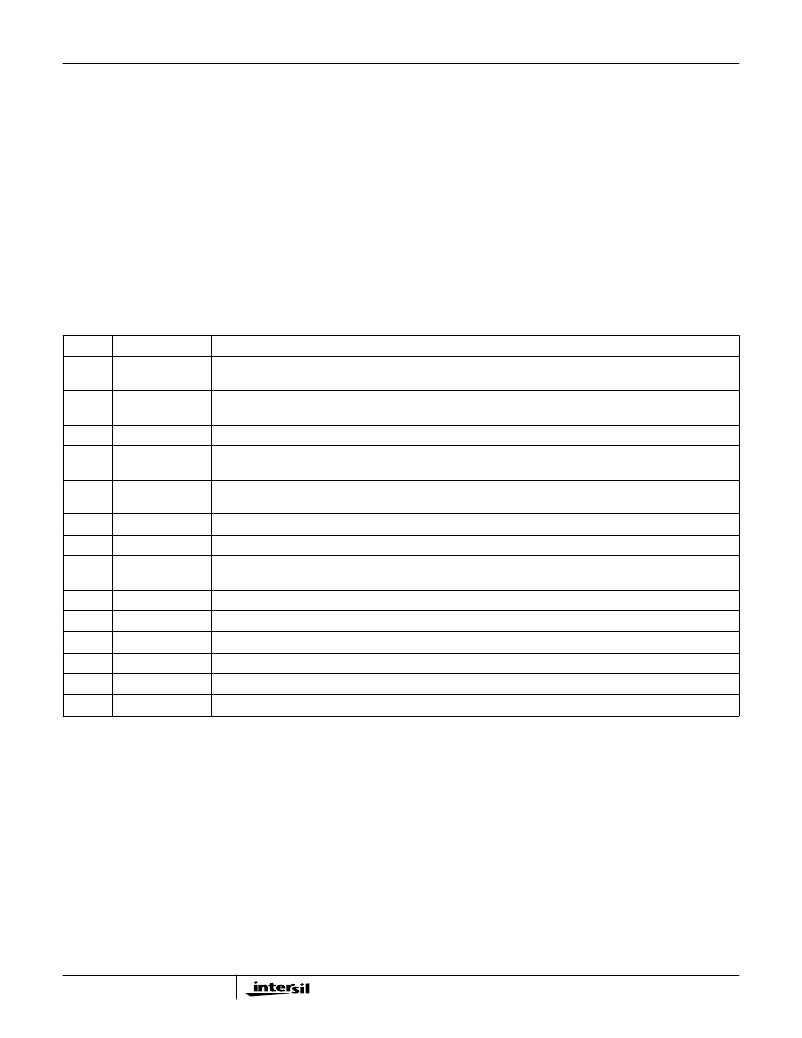

�Appendix� B� Pin� Descriptions�

�weighted� current� sources� representing� each� of� the� ?ve�

�LSBs.� See� the� Functional� Block� Diagram� in� the� datasheet� for�

�a� visual� representation.� To� relate� the� midscale� transition�

�example� to� the� HI5760,� consider� the� following:� The� code�

�0111111111� would� be� represented� by� 15� intermediate�

�current� segments� and� each� of� the� 5� LSB� current� sources� all�

�turned� on.� To� transition� to� code� 1000000000� would� simply�

�require� turning� off� the� 5� LSB� current� sources� and� turning� on�

�the� next� intermediate� current� segment,� bringing� the� total�

�amount� of� current� switching� at� this� ‘major’� code� transition�

�equal� to� the� same� amount� switching� at� 30� other� code�

�transition� points� in� the� code� ramp� from� 0� to� 1023,� so� that� the�

�total� glitch� energy� is� distributed� more� evenly.�

�PIN� NO.�

�1-14�

�15�

�16�

�17�

�18�

�19�

�20,� 25�

�21�

�22�

�23�

�24�

�26�

�27�

�28�

�PIN� NAME�

�D13� (MSB)�

�Through� D0� (LSB)�

�SLEEP�

�REFLO�

�REFIO�

�FSADJ�

�COMP1�

�ACOM�

�IOUTB�

�IOUTA�

�COMP2�

�AV� DD�

�DCOM�

�DV� DD�

�CLK�

�PIN� DESCRIPTION�

�For� the� 14-bit,� HI5960,� these� are� digital� data� bit-13,� (most� significant� bit)� through� digital� data� bit-0,� (least� significant�

�bit).� Pins� 13� and� 14� are� NC� for� the� 12-bit,� HI5860.�

�Control� Pin� for� Power-Down� Mode.� Sleep� mode� is� active� high;� Connect� to� ground� for� normal� mode.� Sleep� pin� has�

�internal� 20� μ� A� active� pull-down� current.�

�Connect� to� analog� ground� to� enable� internal� 1.2V� reference� or� connect� to� AV� DD� to� disable� internal� reference.�

�Reference� voltage� input� if� internal� reference� is� disabled.� Reference� voltage� output� if� internal� reference� is� enabled.� Use�

�0.1� μ� F� cap� to� ground� unless� overdriving� with� a� waveform.�

�Full� Scale� Current� Adjust.� Use� a� resistor� to� ground� to� adjust� full� scale� output� current.� Full� scale� output� current�

�(I� OUTFS� )� =� 32� x� V� FSADJ� /R� SET� ,� (maximum� I� OUTFS� =� 20mA).�

�For� use� in� reducing� noise.� Recommended:� Connect� 0.1� μ� F� from� COMP1� to� AV� DD� .�

�Analog� Ground.�

�The� complementary� current� output� of� the� device.� Full� scale� output� current� is� achieved� when� all� input� bits� are� set�

�to� binary� 0.�

�Current� output� of� the� device.� Full� scale� output� current� is� achieved� when� all� input� bits� are� set� to� binary� 1.�

�Connect� to� ACOM� through� a� 0.1� μ� F� capacitor.�

�Analog� supply� (+3V� to� +5V).�

�Digital� ground.�

�Digital� supply� (+3V� to� +5V).�

�Input� for� clock.� Positive� edge� of� clock� latches� data.�

�3-4�

�相关PDF资料 |

PDF描述 |

|---|---|

| REC5-0505DRW/H2/A | CONV DC/DC 5W 4.5-9VIN +/-05VOUT |

| REC5-483.3DRW/H2/C | CONV DC/DC 5W 36-72VIN +/-3.3V |

| GCM22DCMH | CONN EDGECARD 44POS .156 WW |

| ISL5961EVAL1 | ISL5961 -SOICEVALUATION PLATF |

| REC5-483.3DRW/H2/A | CONV DC/DC 5W 36-72VIN +/-3.3V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI5865 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:12-Bit, 65 MSPS A/D Converter |

| HI5865EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:12-Bit, 65 MSPS A/D Converter |

| HI5865IN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:12-Bit, 65 MSPS A/D Converter |

| HI5905 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:14-Bit, 5MSPS A/D Converter |

| HI5905_03 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:14-Bit, 5MSPS A/D Converter |

发布紧急采购,3分钟左右您将得到回复。