- 您现在的位置:买卖IC网 > PDF目录385381 > HIP2030 (Intersil Corporation) 30V MCT/IGBT Gate Driver(MOS可控硅晶体管/绝缘栅双极晶体管门驱动器) PDF资料下载

参数资料

| 型号: | HIP2030 |

| 厂商: | Intersil Corporation |

| 英文描述: | 30V MCT/IGBT Gate Driver(MOS可控硅晶体管/绝缘栅双极晶体管门驱动器) |

| 中文描述: | 30V的海运码头/ IGBT栅极驱动器(马鞍山可控硅晶体管/绝缘栅双极晶体管门驱动器) |

| 文件页数: | 4/10页 |

| 文件大小: | 94K |

| 代理商: | HIP2030 |

4

HIP2030

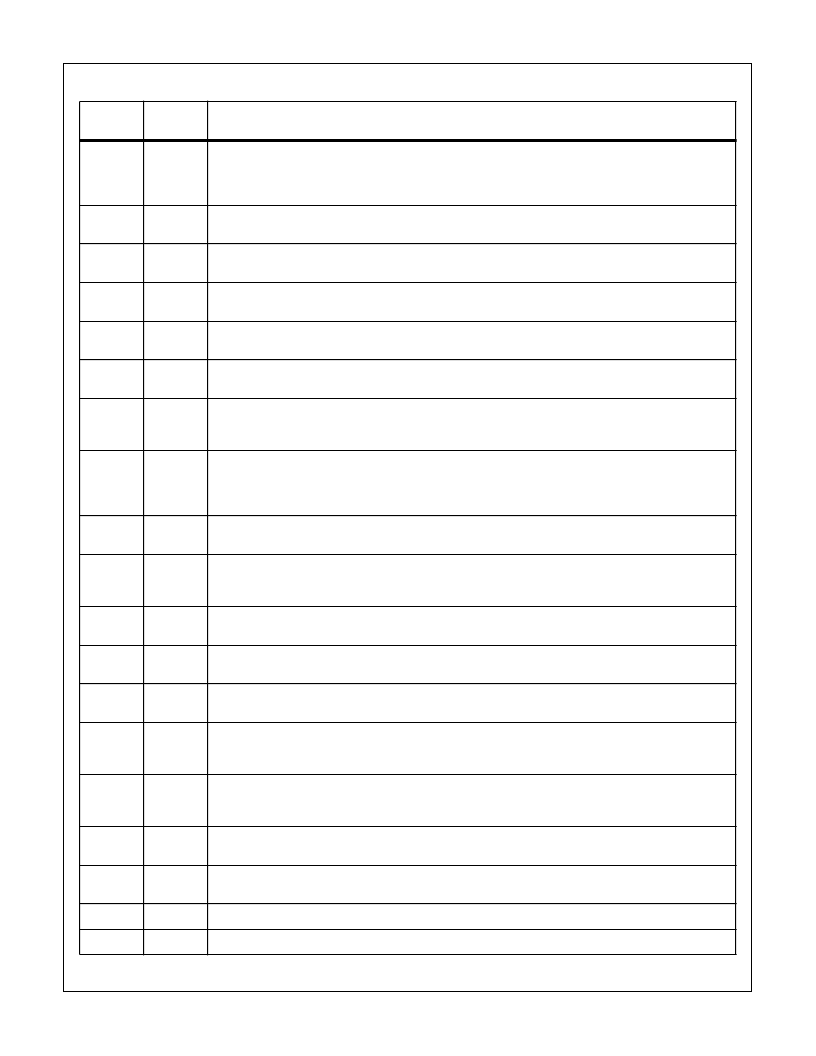

Pin Descriptions

PIN

NUMBER

SYMBOL

DESCRIPTION

1

A-

Negative Comparator input for A channel. This input has a Protected Comparator Input that is clamped to P+

and P- through a 330 ohm resistor. The common mode input voltage, for the Protected Comparator Input, rang-

es from (VP-) +2V and (VP0) +2V. The CMOS output AO (Pin 24) is low when input A- is “True” and input A+ is

“False”.

2

A+

Positive Comparator Input for A channel. The CMOS output AO (Pin 24) is high when input A+ is “True” and

input A- is “False”.

3

B1-

Negative Comparator input for B1 channel. The output of the internal B1-channel comparator is low when input

B1- is “True” and input B1+ is “False”.

4

B1+

Positive Comparator Input for B1 channel. The output of the internal B1-channel comparator is high when input

B1+ is “True” and input B1- is “False”.

5

B2-

Negative Comparator Input for B2 channel. The output of the internal B2-channel comparator is low when input

B2- is “True” and input B2+ is “False”.

6

B2+

Positive Comparator Input for B2 channel. The output of the internal B2-channel comparator is high when input

B2+ is “True” and input B2- is “False”.

7

L-

Negative Comparator Input for L (Latch) channel. Latch mode operation is disabled when L- is “True” and L+ is

“False”. NMOS output LO (Pin 26) is active high in a no latch state. The GO output (Pin 23) is controlled by G-

channel inputs.

8

L+

Positive Comparator Input for L (Latch) channel. Latch mode operation is enabled when L+ is “True” and L- is

“False”. NMOS output LO (Pin 26) is active low in latch state. The GO output (Pin 23) goes to a

“P-MCT OFF” state (VGO = VP+) and is controlled by the internal L-channel latch; which bypasses the G-chan-

nel inputs. Latch mode always overrides the R-channel.

9

R-

Negative Comparator Input for R (Reset) channel. Reset mode, for the internal L-channel latch, is disabled when

R- is “True” and R+ is “False”.

10

R+

Positive Comparator Input for R (Reset) channel. Reset mode, for the internal L-channel latch, is enabled when

R+ is “True” and R- is “False”. Reset mode (enabled) unlatches the internal L-channel latch; which allows the

G-channel inputs to control the GO output (Pin 23). Latch mode must be disabled to operate in reset mode.

11

G-

Negative Comparator Input for G (Main) channel. The G-channel output (Pin 23) goes to a “P-MCT OFF” state

(VGO = VP+) when G- is “True” and G+ is “False”.

12

G+

Positive Comparator Input for G (Main) channel. The G-channel output (Pin 23) goes to a “P-MCT ON” state

(VGO = VP-) when G+ is “True” and G- is “False”.

13

MLT

Input for programmable Minimum Low Time timing capacitor (C

T

). MLT is set by connecting a capacitor between

P0 (Pin 22) and MLT (Pin 13). MLT is approximated by the equation: (C

T

)(5V)/(100uA).

14

MHT

Input for programmable Minimum High Time timing capacitor (C

T

). MHT is set by connecting a capacitor be-

tween P0 (Pin 22) and MHT (Pin 14). MHT is approximated by the equation: (C

T

)(5V)/(100

μ

A). MHT becomes

Minimum Low Time function for turning on N-MCT’s.

15

REG

5V regulator output. An opto-coupler or fiber-optic receiver may be power by connecting the positive voltage pin

of the IC to P0 (Pin 22) and the IC common to REG (Pin 15). The internal regulator (REG) must sink 2mA of

current minimum for the MLT and MHT functions to work properly.

16

P-

Chip negative supply. This pin is generally used as the DC bias power supply common. The regulator transistor,

charge pump and logic are referenced to P- (Pin 16).

17

CPB

Output of the Charge Pump Oscillator Inverter stage. A 0.47

μ

F capacitor is normally connected from this output

to CPA (Pin 19).

18

NC

Unused pin.

19

CPA

Inputofthechargepumpsteeringdiode.A0.47

μ

FcapacitorisnormallyconnectedfromthisinputtoCPB(Pin18).

相关PDF资料 |

PDF描述 |

|---|---|

| HIP2100IB | 100V/2A Peak, Low Cost, High Frequency Half Bridge Driver |

| HIP5015EVAL2 | () |

| HIP5060DW | Power Control IC Single Chip PowerSupply |

| HIP5060DY | FPGA 1000000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP6003 | Buck Pulse-Width Modulator (PWM) Controller and Output Voltage Monitor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP2030B4 WAF | 制造商:Harris Corporation 功能描述: |

| HIP2030EVAL | 制造商:Harris Corporation 功能描述: |

| HIP2060 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:60V, 10A Half Bridge Power MOSFET Array |

| HIP2060 WAF | 制造商:Intersil Corporation 功能描述: |

| HIP2060AS1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:60V, 10A Half Bridge Power MOSFET Array |

发布紧急采购,3分钟左右您将得到回复。