- 您现在的位置:买卖IC网 > PDF目录371821 > HIP6028 (Intersil Corporation) Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface PDF资料下载

参数资料

| 型号: | HIP6028 |

| 厂商: | Intersil Corporation |

| 元件分类: | 基准电压源/电流源 |

| 英文描述: | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

| 中文描述: | 先进的双PWM和线性电源控制集成接口ACPI支持 |

| 文件页数: | 8/16页 |

| 文件大小: | 140K |

| 代理商: | HIP6028 |

2-318

over-voltage on the PWM output disables all converters and

drives the FAULT pin to VCC.

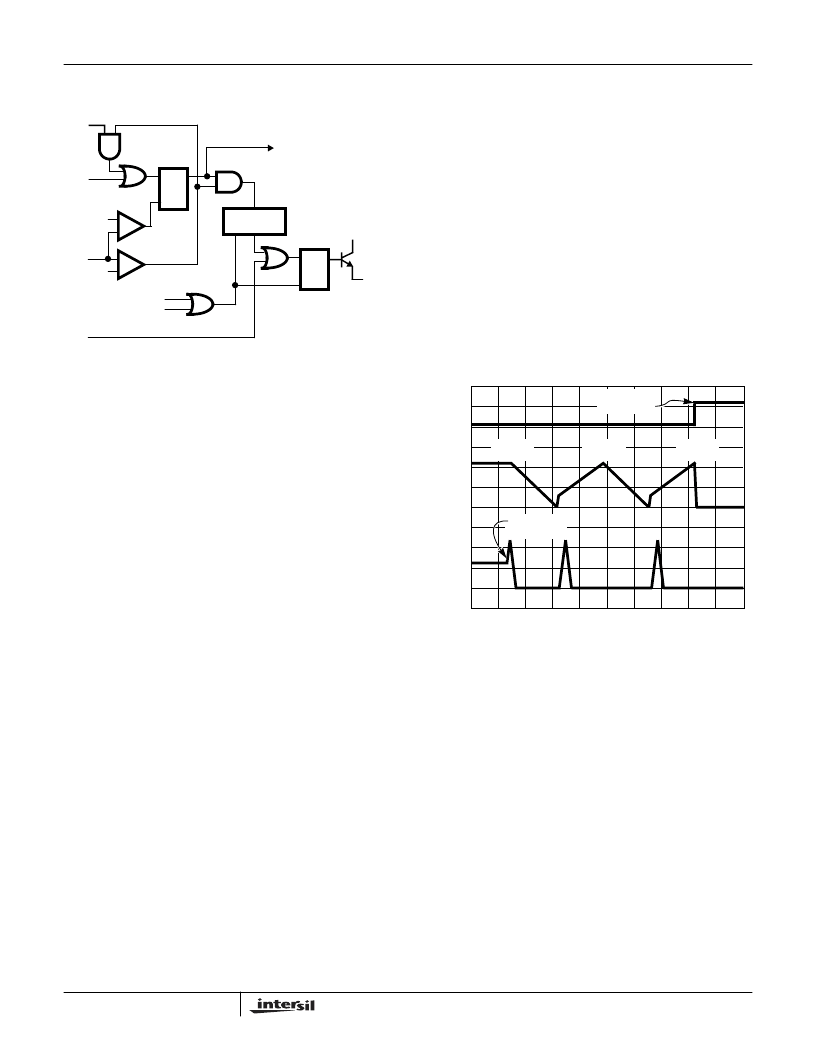

Figure 7 shows a simplified schematic of the fault logic. An

over-voltage detected on VSEN1 immediately sets the fault

latch. A sequence of three over-current fault signals also

sets the fault latch. A comparator indicates when C

SS

is fully

charged (UP signal), such that an under-voltage event on

either linear output (FB2 or FB3) is ignored until after the

soft-start interval (T4 in Figure 6). At startup, this allows

V

OUT3

to slew up without generating a fault. Cycling the bias

input voltage (+12V

IN

on the VCC pin) off then on resets the

counter and the fault latch. Shutting down VOUT1 and

VOUT3 also resets the counter and latch.

Over-Voltage Protection

During operation, a short on the upper PWM MOSFET (Q1)

causes V

OUT1

to increase. When the output exceeds the

over-voltage threshold of 115% (typical) of DACOUT, the

over-voltage comparator trips to set the fault latch and turns

Q2 on as required in order to regulate V

OUT1

to 1.15 x

DACOUT. This blows the input fuse and reduces V

OUT1

.

The fault latch raises the FAULT pin close to VCC potential.

A separate over-voltage circuit provides protection during

the initial application of power. For voltages on the VCC pin

below the power-on reset (and above ~4V), V

OUT1

is

monitored for voltages exceeding 1.26V. Should VSEN1

exceed this level, the lower MOSFET (Q2) is driven on as

needed to regulate V

OUT1

to 1.26V.

Over-Current Protection

All outputs are protected against excessive over-currents.

The PWM controller uses the upper MOSFET’s on-

resistance, r

DS(ON)

to monitor the current for protection

against shorted outputs. The linear regulator restricts the

current through the integrated power device to 230mA

(typically). The linear regulator and the linear controller

monitor VOUT2 and VSEN3, respectively, for under-voltage

to protect against excessive currents.

Figures 8 and 9 illustrate the over-current protection with an

overload on V

OUT1

. The overload is applied at T0 and the

current increases through the output inductor (L

OUT1

). At

time T1, the OVER-CURRENT1 comparator trips when the

voltage across Q1 (I

D

r

DS(ON)

) exceeds the level

programmed by R

OCSET

. This inhibits all outputs,

discharges the soft-start capacitor (C

SS

) with an 11

μ

A

current sink, and increments the counter. C

SS

recharges at

T2 and initiates a soft-start cycle with the error amplifiers

clamped by soft-start. With OUT1 still overloaded, the

inductor current increases to trip the over-current

comparator. Again, this inhibits all outputs, but the soft-start

voltage continues increasing to 4V before discharging. The

counter increments to 2. The soft-start cycle repeats at T3

and trips the over-current comparator. The SS pin voltage

increases to 4V at T4 and the counter increments to 3. This

sets the fault latch to disable the converter. The fault is

reported on the FAULT pin.

The linear regulator and linear controller monitor the outputs

for an under-voltage. Should excessive currents cause

VOUT2 or VSEN3 to fall below the linear under-voltage

threshold, the LUV signal sets the over-current latch if C

SS

is

fully charged. Blanking the LUV signal during the C

SS

charge

interval allows the linear outputs to build above the under-

voltage threshold during normal start-up. Cycling the bias

input power off then on resets the counter and the fault latch.

Resistor R

OCSET

programs the over-current trip level for the

PWM converter. As shown in Figure 9, the internal 200

μ

A

current sink develops a voltage across R

OCSET

(V

SET

) that

is referenced to V

IN

. The DRIVE signal enables the over-

current comparator (OVER-CURRENT1). When the voltage

across the upper MOSFET (V

DS(ON)

) exceeds V

SET

, the

over-current comparator trips to set the over-current latch.

Both V

SET

and V

DS

are referenced to V

IN

and a small

capacitor across R

OCSET

helps V

OCSET

track the variations

FAULT

LATCH

S

R

Q

POR

SD1&3

COUNTER

OC1

OV

LUV

+

-

+

-

0.15V

4V

SS

VCC

FAULT

R

FIGURE 7. FAULT LOGIC - SIMPLIFIED SCHEMATIC

UP

OVER

CURRENT

LATCH

INHIBIT

S

R

Q

S

0A

0V

2V

4V

FIGURE 8. OVER-CURRENT OPERATION

TIME

T1

T2

T3

T0

T4

F

0V

10V

OVERLOAD

APPLIED

C= 1

C= 2

C= 3

FAULT

REPORTED

HIP6028

相关PDF资料 |

PDF描述 |

|---|---|

| HIP6028CB | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

| HIP6303CB-T | Microprocessor CORE Voltage Regulator Multi-Phase Buck PWM Controller |

| HIP6303 | Microprocessor CORE Voltage Regulator Multi-Phase Buck PWM Controller(微处理器核心电压稳压多相冲跳脉宽调制控制器) |

| HIP6303CB | Microprocessor CORE Voltage Regulator Multi-Phase Buck PWM Controller |

| HIP6303EVAL1 | Microprocessor CORE Voltage Regulator Multi-Phase Buck PWM Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP6028CB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6028CB WAF | 制造商:Harris Corporation 功能描述: |

| HIP6028EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface |

| HIP6034CB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| HIP6034CB-T | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

发布紧急采购,3分钟左右您将得到回复。