- 您现在的位置:买卖IC网 > PDF目录1996 > HMC704LP4E (Hittite Microwave Corporation)IC FRACT-N PLL 16BIT 24QFN PDF资料下载

参数资料

| 型号: | HMC704LP4E |

| 厂商: | Hittite Microwave Corporation |

| 文件页数: | 16/44页 |

| 文件大小: | 0K |

| 描述: | IC FRACT-N PLL 16BIT 24QFN |

| 标准包装: | 1 |

| 类型: | 整数 N/小数 N 分频 |

| PLL: | 是 |

| 输入: | CMOS |

| 输出: | CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 8GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.3V,5V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-VQFN 裸露焊盘 |

| 供应商设备封装: | 24-QFN 裸露焊盘(4x4) |

| 包装: | 标准包装 |

| 其它名称: | 1127-1066-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

P

LL

s

-

s

M

T

5 - 23

HMC704LP4E

v03.1211

8 GHz fractionaL-n PLL

For price, delivery, and to place orders: Hittite Microwave Corporation,20 Alpha Road, Chelmsford, MA 01824

Phone: 978-250-3343

Fax: 978-250-3373

Order On-line at www.hittite.com

Application Support: Phone: 978-250-3343 or apps@hittite.com

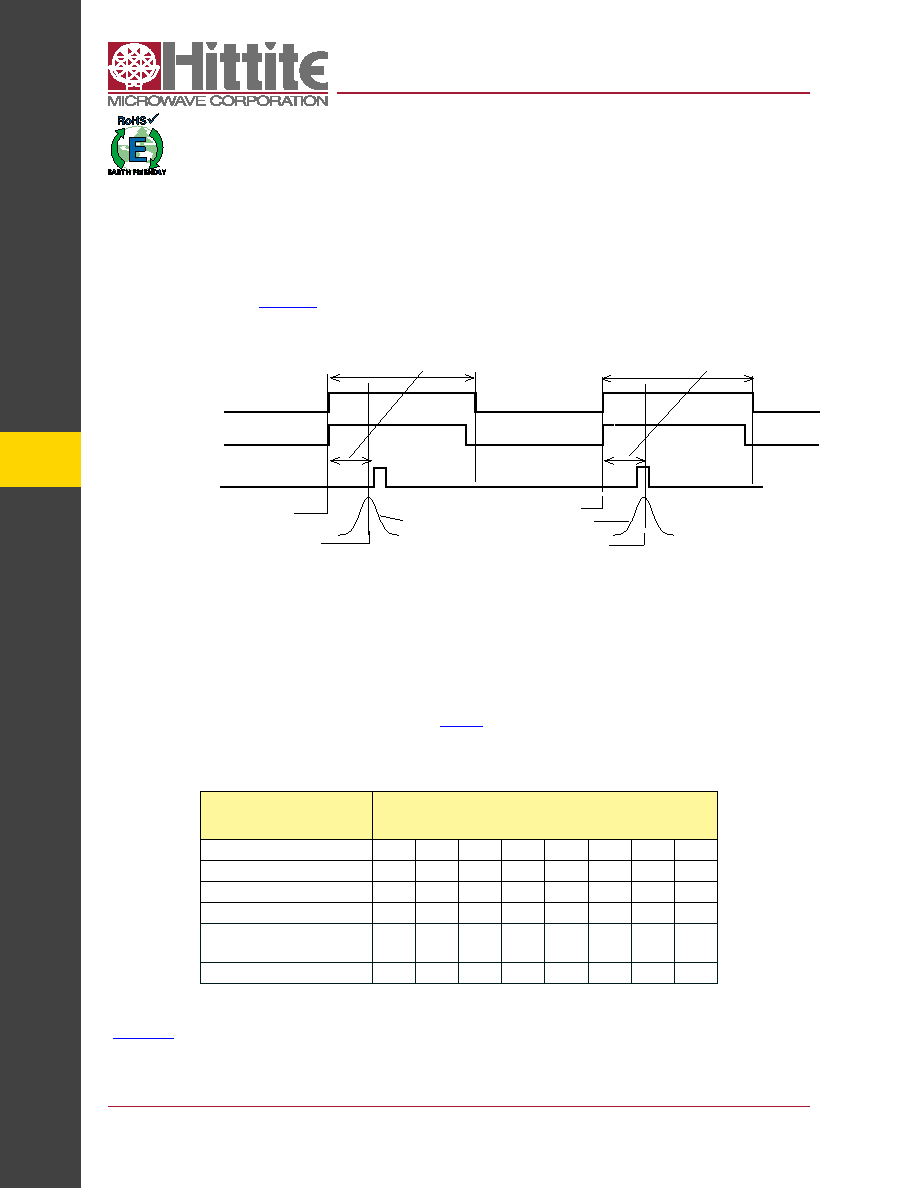

Lock Detect operation with Phase offset

When operating in fractional mode the linearity of the charge pump and phase detector are much more critical than in

integer mode. The phase detector linearity degrades when operated with zero phase offset. Hence in fractional mode it

is necessary to offset the phase of the reference and VCO at the phase detector. In such a case, for example with an

offset delay, as shown in Figure 32, the VCO arrival may always occur after the reference. The lock detect circuit win-

dow may need to be adjusted to allow for the delay being used, if the delay is large.

VCO AT PD with FRAC Jitter

LOCK

DETECT

WINDOW

Twindow ~ +10nsec

Figure 32. Lock Detect Window - Fractional Mode with Offset

REF PHAsE ARRIVAL

FRACTIONAL MODE

VCO ARRIVAL DIsTRIBUTION AT PD

PHAsE JITTER

LOCK WINDOW

AVG VCO PHAsE OFFsET

AVG PHAsE OFFsET

FRACTIONAL MODE

AVG VCO PHAsE OFFsET

REF PHAsE ARRIVAL

AVG PHAsE OFFsET

AT PD

In integer mode, 0 offset is recommended. In fractional mode, the time offset should be set to ~ 2.5ns + 4Tps, where Tps

is the RF period at the fractional prescaler input (i.e. after the optional fixed divide by 2). Refer to the Fractional Opera-

tion section for further details about calculating charge pump offset currents

Digital Lock Detect with Digital Window Example

Typical Digital Lock detect window widths are shown in Table 7. Lock Detect windows typically vary +/-10% vs voltage

and +/-15% over -40C to +85C.

table 7. typical Digital Lock Detect Window

LD Timer speed

Reg07[11:10]

Digital Lock Detect Window

Nominal Value +/-25%

(nsec)

Fastest 00

6.5

8.0

11.0

17

29

53

100

195

01

7.0

8.9

12.8

21

36

68

130

255

10

7.1

9.2

13.3

22

38

72

138

272

slowest 11

7.6

10.2

15.4

26

47

88

172

338

LD Timer Divider setting

Reg07[9:7]

0

1

2

3

4

5

6

7

LD Timer Divider Value

0.5

1

2

4

8

16

32

64

As an example if we operate in fractional mode, with a 50MHz PD, a 2700 MHz VCO and a Charge pump gain of 2mA

(“Reg 09h”), based on the previous example, we should set the DC phase offset near 2.5ns+4x370ps =4ns, or 20% of

the 20ns reference period. It becomes a larger proportion with increasing fpd. The offset current is therefore 20% x

2mA=400uA. The polarity of the offset should be chosen so that the VCO lags the reference for the most consistent

results. For non-inverting /inverting loop filter configurations, we recommend down/up offsets, respectively.

REFERENCE

sIGNAL

相关PDF资料 |

PDF描述 |

|---|---|

| HMC830LP6GE | IC FRACT-N PLL W/VCO 40QFN |

| HMP8117CNZ | IC VIDEO DECODER NTSC/PAL 80PQFP |

| HMP8156ACNZ | IC VIDEO ENCODER NTSC/PAL 64MQFP |

| HSP45102SC-40Z | IC OSC NCO 40MHZ 28-SOIC |

| HSP45106JC-33Z | IC OSC NCO 33MHZ 84-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMC704LP4ETR | 制造商:Hittite Microwave Corp 功能描述:IC FRACT-N PLL 16BIT 24QFN |

| HMC705LP4 | 制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:6.5 GHz PROGRAMMABLE DIVIDER (N = 1 - 17) |

| HMC705LP4E | 制造商:Hittite Microwave Corp 功能描述:IC DIVIDER HBT PROGR 24-QFN |

| HMC705LP4ETR | 功能描述:IC DIVIDER HBT PROGR 24QFN 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 功能:分频器 频率:100MHz ~ 6.5GHz RF 类型:- 辅助属性:- 封装/外壳:24-VFQFN 裸露焊盘 供应商器件封装:24-QFN(4x4) 标准包装:1 |

| hmc706lc3c | 制造商:Hittite Microwave Corp 功能描述:IC CONV NRZ-RZ 13GBPS 16SMD |

发布紧急采购,3分钟左右您将得到回复。