- 您现在的位置:买卖IC网 > PDF目录370643 > HMN12816D (Electronic Theatre Controls, Inc.) Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V PDF资料下载

参数资料

| 型号: | HMN12816D |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| 中文描述: | 非易失性SRAM模块即可移植(128K的x 16位),40pin浸,5V的 |

| 文件页数: | 5/9页 |

| 文件大小: | 143K |

| 代理商: | HMN12816D |

HANBit

HMN12816D

URL : www.hbe.co.kr 5 HANBit Electronics Co.,Ltd

Rev. 0.0 (April, 2002)

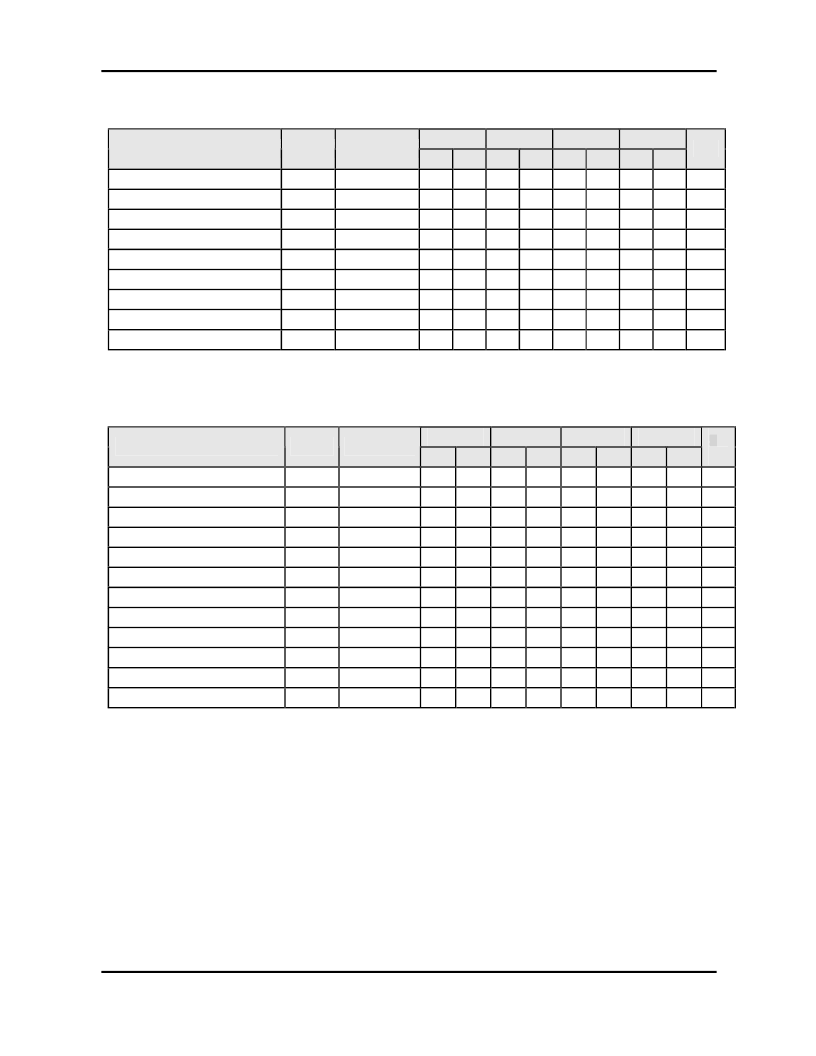

READ CYCLE

(T

A

= T

OPR

, V

CCmin

≤

V

CC

≤

V

CCmax

)

-70

-85

-120

-150

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

Read Cycle Time

t

RC

70

-

85

-

120

-

150

-

ns

Address Access Time

t

ACC

Output load A

-

70

-

85

-

120

-

150

ns

Chip enable access time

t

ACE

Output load A

-

70

-

85

-

120

-

150

ns

Output enable to Output valid

t

OE

Output load A

-

35

-

45

-

60

-

70

ns

Chip enable to output in low Z

t

CLZ

Output load B

5

-

5

-

5

-

10

-

ns

Output enable to output in low Z

t

OLZ

Output load B

5

-

0

-

0

-

5

-

ns

Chip disable to output in high Z

t

CHZ

Output load B

0

25

0

35

0

45

0

60

ns

Output disable to output high Z

t

OHZ

Output load B

0

25

0

25

0

35

0

50

ns

Output hold from address change

t

OH

Output load A

10

-

10

-

10

-

10

-

ns

WRITE CYCLE

(T

A

= T

OPR

, V

ccmin

≤

V

cc

≤

V

ccmax

)

-70

-85

-120

-150

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

MIN

MAX

MIN

MAX

Min

Max

UNI

T

Write Cycle Time

t

WC

70

-

85

-

120

-

150

-

ns

Chip enable to end of write

t

CW

Note 1

65

-

75

-

100

-

100

-

ns

Address setup time

t

AS

Note 2

0

-

0

-

0

-

0

-

ns

Address valid to end of write

t

AW

Note 1

65

-

75

-

100

-

90

-

ns

Write pulse width

t

WP

Note 1

55

-

65

-

85

-

90

-

ns

Write recovery time (write cycle 1)

t

WR1

Note 3

5

-

5

-

5

-

5

-

ns

Write recovery time (write cycle 2)

t

WR2

Note 3

15

-

15

-

15

-

15

-

ns

Data valid to end of write

t

DW

30

-

35

-

45

-

50

-

ns

Data hold time (write cycle 1)

t

DH1

Note 4

0

-

0

-

0

-

0

-

ns

Data hold time (write cycle 2)

t

DH2

Note 4

10

-

10

-

10

-

0

-

ns

Write enabled to output in high Z

t

WZ

Note 5

0

25

0

30

0

40

0

50

ns

Output active from end of write

t

OW

Note 5

5

-

0

-

0

-

5

-

ns

NOTE:

1. A write ends at the earlier transition of /CE going high and /WE going high.

2. A write occurs during the overlap of allow /CE and a low /WE. A write begins at the later transition of /CE

going low and /WE going low.

3. Either t

WR1

or t

WR2

must be met.

4. Either t

DH1

or t

DH2

must be met.

5. If /CE goes low simultaneously with /WE going low or after /WE going low, the outputs remain in high-

impedance state.

相关PDF资料 |

PDF描述 |

|---|---|

| HMN12816D-120 | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-120I | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-150 | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-70 | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-150I | Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMN12816D-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-120I | 制造商:HANBIT 制造商全称:Hanbit Electronics Co.,Ltd 功能描述:Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-150 | 制造商:HANBIT 制造商全称:Hanbit Electronics Co.,Ltd 功能描述:Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-150I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

| HMN12816D-70 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Non-Volatile SRAM MODULE 2Mbit (128K x 16-Bit), 40pin-Dip, 5V |

发布紧急采购,3分钟左右您将得到回复。