- 您现在的位置:买卖IC网 > PDF目录370643 > HMP8112ACN (Harris Corporation) NTSC/PAL Video Decoder PDF资料下载

参数资料

| 型号: | HMP8112ACN |

| 厂商: | Harris Corporation |

| 英文描述: | NTSC/PAL Video Decoder |

| 中文描述: | NTSC / PAL视频解码器 |

| 文件页数: | 6/40页 |

| 文件大小: | 563K |

| 代理商: | HMP8112ACN |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

6

Introduction

The HMP8112 is an NTSC/PAL compatible Video Decoder

with both chroma burst and line locked digital phase locked

loops. The HMP8112 contains two 8-bit A/D converters and

an I

2

C port for programming internal registers.

Analog Video/Mux Inputs

The Luminance channel has three analog video inputs that

can be used for composite or the Y input of a S-Video signal,

and one analog input for chrominance. LIN2 is used with CIN

to interface an S-Video input. Three composite or two com-

posite and one S-Video inputs can be applied to the

HMP8112 at any one time. Control of the analog front end is

selected by bits 2 and 1 of the Video Input Control Register.

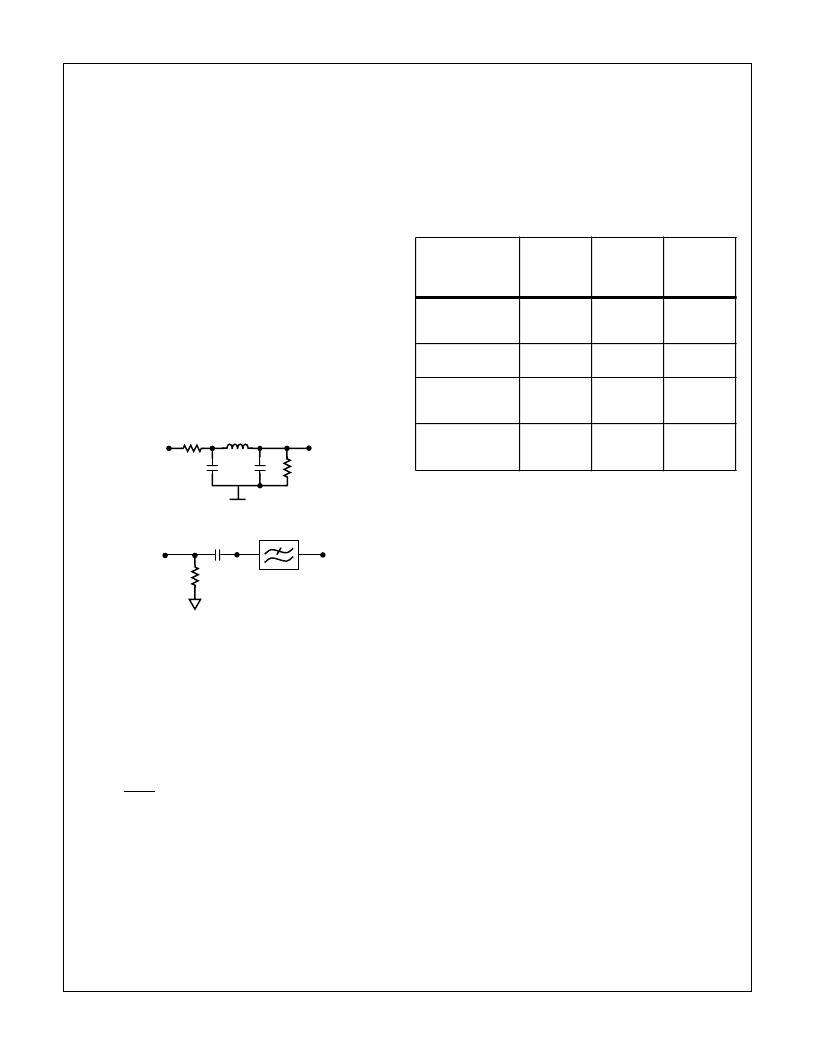

Anti-Aliasing Filter

An external anti-alias filter is required to achieve optimum

performance and prevent high frequency components from

being aliased back into the video image. For the LIN inputs a

single filter is connected to L_OUT and L_ADIN. For CIN the

anti-aliasing filter should be connected to the CIN input. A

recommended filter is shown below.

AGC And Clamp Circuit

Inputs LIN0-2 contain a sync tip AGC amplifier. During the

sync tip the value of the A/D is driven to code 0 by gaining up

the video input signal. The sync tip AGC is sampled during the

HAGC pulse time which is controlled by the HAGC Pulse Start

Time and End Time registers. The LIN0-2 inputs apply a DC

clamp reference to the back porch of the video. This is con-

trolled by the DC-RESTORE Pulse Start Time and End Time

Registers.

After a

RESET

, a change of the video standard, or a PLL

Chrominance Subcarrier Ratio Register load, HAGC and DC

RESTORE are overlapped, until LOCKED is asserted. (the

PLL has acquired a stable line lock). This is the acquisition

mode of the PLL where the decoder is trying to lock to a new

video source. Once the PLL is LOCKED, HAGC and DC

RESTORE are moved out to the default programmed values

in the user programming registers. The HAGC should be set

coincident to the incoming horizontal sync signal. The HAGC

pulse should be set to a width of 2

μ

s.

Once the PLL is locked the DC RESTORE signal is moved

out to the default programmed values in the user program-

ming registers. The DC RESTORE pulse can be pro-

grammed with the DC RESTORE Start and End time control

registers. DC RESTORE should be asserted 6.5

μ

s after the

falling edge of horizontal sync (0

HSYNC

) and held for a dura-

tion of 2

μ

s. Both HAGC and DC RESTORE are synchronous

to the output sample rate (OSR) converter and are clocked

in OSR (pixel clock) clock periods. The OSR clock rate is

dependent on the input standard used. See Table 1 for the

register values used for the different video standards.

White Peak Enable

The white peak enable input, (WPE) enables or disables the

white peak control. Enabled, (logic high) when the digital

outputs exceed code 248, the AGC will reduce the gain of

the video amplifier to prevent over-ranging the A/D. If dis-

abled, the AGC operates normally, keeping the horizontal

sync tip at code 0 and allowing the A/D’s range to go to 255

at the maximum peak input.

NTSC/PAL Decoder

The NTSC/PAL decoder is designed to convert incoming

Composite or Separated (SVHS, Y/C) video into it’s YCbCr

component parts. The digital phase locked loops are

designed to synchronize to the various NTSC/PAL stan-

dards. They provide a stable internal 4xf

SC

(Frequency of

the Color Sub-Carrier) video clock for color demodulation,

and a line locked clock for vertical spatial pixel alignment.

The decoder uses the CLK to run the A/D converters and the

phase locked loops. This asynchronous master clock for the

decoder eliminates the need for a unique clock source in a Mul-

timedia application. CLK can run from 20MHz to 30MHz when

using the 16-bit Synchronous Data output Mode. The user

must program the CLK to Color Sub-Carrier Ratio to match the

CLK frequency used (see Internal Phase Locked Loops discus-

sion). When using the 8-bit Burst Data Output Mode the CLK

should be a 24.5454MHz, 27MHz or 29.5MHz depending on

the output video standard chosen. The crystal oscillator must

have a

±

50ppm accuracy and a 60/40% duty cycle symmetry to

ensure proper operation. Since the video data from the external

A/D’s are sampled at the CLK frequency a sample rate con-

verter is employed to convert the data from the CLK rate to the

AGND

680

82

μ

H

15pF

15pF

5.62k

L_OUT

(PIN 9)

L_ADIN

(PIN 8)

CIN

(PIN 19)

75

1.0

μ

F

CHROMA

IN

FIGURE 1. RECOMMENDED ANTI-ALIASING FILTER

LOW PASS FILTER

TABLE 1. HAGC AND DC RESTORE VALUES

VIDEO

OUTPUT

STANDARD

HAGC

START/END

VALUES

DC

RESTORE

START/END

VALUES

HSYNC

START/END

VALUES

Square Pixel

NTSC

640x480

02F8/0008

H

0028/0040

H

0020/0050

H

CCIR601 NTSC

720x480

033F/0000

H

0037/0052

H

033B/0060

H

CCIR601

PAL

720X512

033F/0000

H

0037/0052

H

033B/0060

H

Square Pixel

PAL

768X512

03A0/0018

H

0040/0054

H

0020/0070

H

HMP8112

相关PDF资料 |

PDF描述 |

|---|---|

| HMP8112CN | NTSC/PAL Video Decoder |

| HMP8112EVAL2 | NTSC/PAL Video Decoder |

| HMP8156EVAL2 | NTSC/PAL Video Decoder |

| HMP8156EVAL1 | NTSC/PAL Encoders |

| HMP8156EVAL2 | NTSC/PAL Encoders |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMP8112CN | 制造商:HARRIS 制造商全称:HARRIS 功能描述:NTSC/PAL Video Decoder |

| HMP8112EVAL1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8112EVAL2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8115 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8115CN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

发布紧急采购,3分钟左右您将得到回复。