- 您现在的位置:买卖IC网 > PDF目录370643 > HMP8112ACN (Harris Corporation) NTSC/PAL Video Decoder PDF资料下载

参数资料

| 型号: | HMP8112ACN |

| 厂商: | Harris Corporation |

| 英文描述: | NTSC/PAL Video Decoder |

| 中文描述: | NTSC / PAL视频解码器 |

| 文件页数: | 8/40页 |

| 文件大小: | 563K |

| 代理商: | HMP8112ACN |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

8

phase alternates from line to line by 90

o

. To fully separate

the PAL chrominance and luminance signals the user select-

able filters should be enabled. The chroma notch filter built

into the luminance channel should be enabled for PAL sys-

tems to reduce cross luminance effects. The low pass filter

in the chrominance processing chain helps to reduce cross

color products.

The demodulator in the decoder decodes the color compo-

nents into U and V. The U and V components are converted

to Cb and Cr components after the decoding process.

YCbCr has a usable data range as shown in Figure 4. The

data range for Y is limited to a minimum of 16.

The decoder is compatible with all NTSC and PAL video for-

mats available throughout the world. Table 2 shows the com-

patible video standards.

Horizontal Sync Detection

Horizontal sync is detected in the Output Sample Rate con-

verter (OSR). The OSR spatially aligns the pixels in the verti-

cal direction by using the horizontal sync information

embedded in the digital video data stream. The HSYNC

sync pulse out of the decoder is a video synchronous output

pin. This signal follows the horizontal sync of an input video

source. If there is no source the HSYNC pin will continue to

run at video rates due to the Line Locked PLL free-running.

HSYNC can be moved throughout the video line using the

HSYNC Start and End time registers. This 10-bit register

allows the HSYNC to be moved in OSR clock increments

(12.27MHZ, 13.5MHz or 14.75MHz).

Vertical Sync And Field Detection

The vertical sync and field detect circuit of the decoder uses

a low time counter to detect the vertical sync sequence in

the video data stream. The low time counter accumulates

the low time encounted after the horizontal sync edge or at

the start of each line. When the low time count exceeds the

vertical

sync

detect

threshold,

immediately. VSYNC will remain asserted for a minimum of 1

line. The FIELD flag is updated at the same time as the

VSYNC line. The FIELD pin is a ‘0’ for ODD fields and a ‘1’

for even fields.

VSYNC

is

asserted

In the case of lost vertical sync or excessive noise that would

prevent the detection of vertical sync, the FIELD flag will

continue to toggle. Lost vertical sync is declared if after 337

lines a vertical sync period was not detected for 3 succes-

sive lines. When this occurs the phase locked loops are ini-

tialized to the acquisition state.

The VSYNC pulse out of the decoder follows the vertical

sync detection and is typically 6.5 lines long. The VSYNC

will run at the field rate of the selected video standard

selected. For NTSC the field rate is 60Hz and for PAL the

field rate is 50Hz. This signal will continue to run even in the

event of no incoming video signal.

Internal Phase Locked Loops

The HMP8112 has two independent digital phase locked

loops on chip. A chroma phase-locked loop is implemented

to maintain chroma lock for demodulation of the color chan-

nel, and a line locked phase lock loop is implemented to

maintain vertical spatial alignment. The phase locked loops

are designed to maintain lock even in the event of VCR

headswitches and multipath noise.

The HMP8112 can use a main crystal (CLK) of 20MHz to

30MHz. The crystal is used as a reference frequency for the

internal phase locked loops. The ratio of the crystal fre-

quency to the video standard is programmed into an internal

register for the PLLs to correctly decode video.

The HMP8112 decoder contains 2 sample rate converters

and 2 phase locked loops that lock to the incoming video. The

input sample rate converter synchronizes the digitized video

from the CLK rate to a 4xf

SC

rate. The chrominance is sepa-

rated from the luminance and then demodulated. The Chroma

phase locked loop uses the CLK source as the PLL reference

frequency. To initialize the chroma PLL, the CLK to 4xf

SC

ratio

must be loaded. For example, if the CLK was 27MHz and the

video signal is NTSC (4 x 3.579545MHz = 14.318MHz) then

the ratio loaded is 0.5302895 in 16-bit precision.

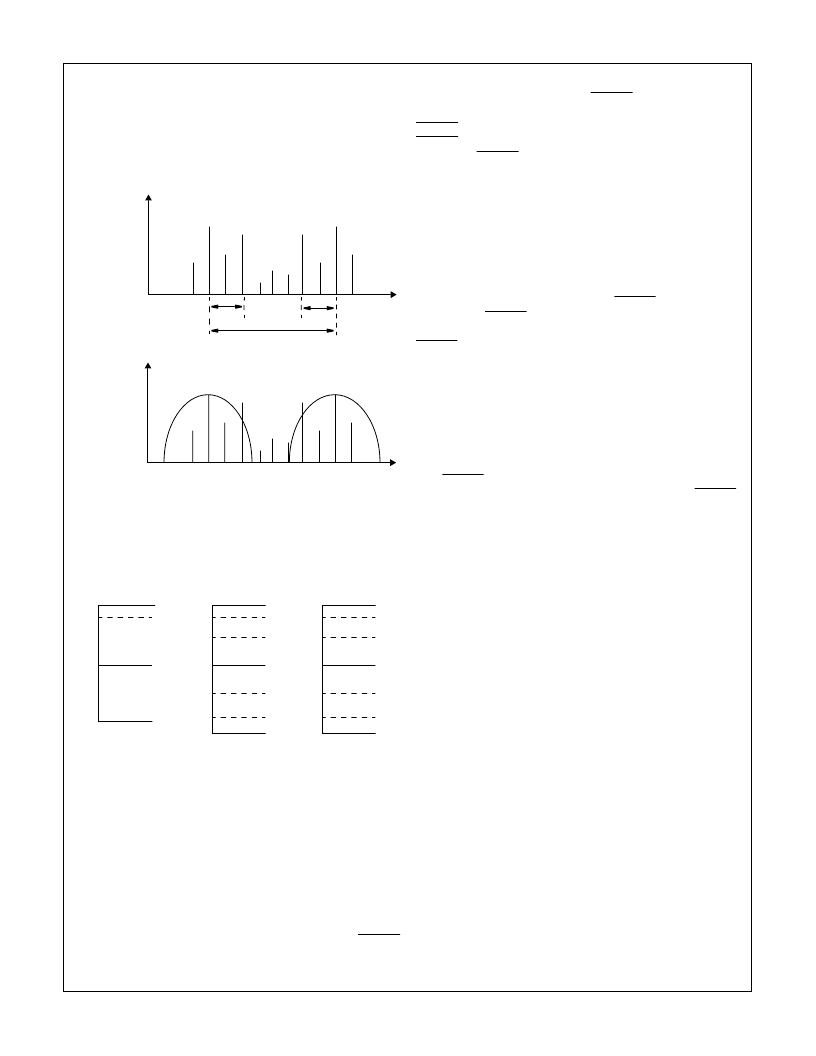

FREQUENCY

AMPLITUDE

f

H

/4

f

H

Y

I, Q

Y

FREQUENCY

AMPLITUDE

Y

Y

f

H

/4

I, Q

I, Q

I, Q

FIGURE 5. COMPOSITE PAL INTERLEAVE SCHEME

Y DATA

RANGE

Cb DATA

RANGE

Cr DATA

RANGE

16

128

248

255

0

16

128

240

255

0

16

128

240

255

212

44

212

44

BLACK

WHITE

100%

BLUE

100%

BLUE

75%

YELLOW

100%

YELLOW

75%

RED

100%

RED

75%

CYAN

100%

CYAN

75%

FIGURE 6. YCbCr DATA RANGES

HMP8112

相关PDF资料 |

PDF描述 |

|---|---|

| HMP8112CN | NTSC/PAL Video Decoder |

| HMP8112EVAL2 | NTSC/PAL Video Decoder |

| HMP8156EVAL2 | NTSC/PAL Video Decoder |

| HMP8156EVAL1 | NTSC/PAL Encoders |

| HMP8156EVAL2 | NTSC/PAL Encoders |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMP8112CN | 制造商:HARRIS 制造商全称:HARRIS 功能描述:NTSC/PAL Video Decoder |

| HMP8112EVAL1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8112EVAL2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8115 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8115CN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

发布紧急采购,3分钟左右您将得到回复。