参数资料

| 型号: | HS1-3182-9+ |

| 厂商: | Intersil |

| 文件页数: | 6/7页 |

| 文件大小: | 0K |

| 描述: | IC LN-DRVR ARINC 429 16-SBDIP |

| 标准包装: | 23 |

| 类型: | 线路驱动器,发射器 |

| 驱动器/接收器数: | 2/0 |

| 电源电压: | 13.5 V ~ 16.5 V |

| 安装类型: | 通孔 |

| 封装/外壳: | 16-CDIP(0.300",7.62mm) |

| 供应商设备封装: | 16-CDIP 侧面铜焊 |

| 包装: | 管件 |

6

FN2963.3

May 30, 2008

HS-3182

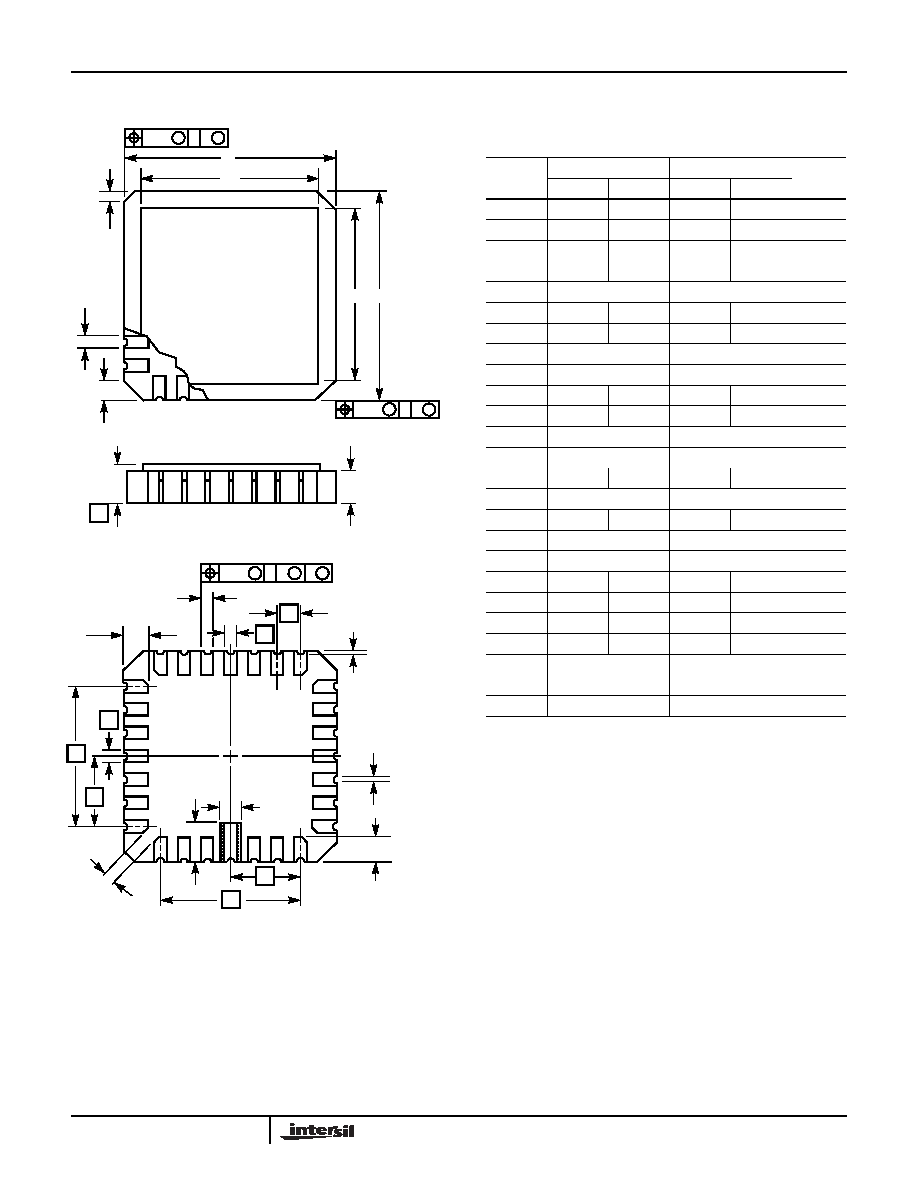

Ceramic Leadless Chip Carrier Packages (CLCC)

D

j x 45o

D3

B

h x 45o

A

A1

E

L

L3

e

B3

L1

D2

D1

e1

E2

E1

L2

PLANE 2

PLANE 1

E3

B2

0.010

E H

S

0.010

E F

S

-E-

0.007

E F

M

S HS

B1

-H-

-F-

J28.A MIL-STD-1835 CQCC1-N28 (C-4)

28 PAD CERAMIC LEADLESS CHIP CARRIER PACKAGE

SYMBOL

INCHES

MILLIMETERS

NOTES

MIN

MAX

MIN

MAX

A

0.060

0.100

1.52

2.54

6, 7

A1

0.050

0.088

1.27

2.23

-

B

----

-

B1

0.022

0.028

0.56

0.71

2, 4

B2

0.072 REF

1.83 REF

-

B3

0.006

0.022

0.15

0.56

-

D

0.442

0.460

11.23

11.68

-

D1

0.300 BSC

7.62 BSC

-

D2

0.150 BSC

3.81 BSC

-

D3

-

0.460

-

11.68

2

E

0.442

0.460

11.23

11.68

-

E1

0.300 BSC

7.62 BSC

-

E2

0.150 BSC

3.81 BSC

-

E3

-

0.460

-

11.68

2

e

0.050 BSC

1.27 BSC

-

e1

0.015

-

0.38

-

2

h

0.040 REF

1.02 REF

5

j

0.020 REF

0.51 REF

5

L

0.045

0.055

1.14

1.40

-

L1

0.045

0.055

1.14

1.40

-

L2

0.075

0.095

1.90

2.41

-

L3

0.003

0.015

0.08

0.038

-

ND

7

3

NE

7

3

N28

28

3

Rev. 0 5/18/94

NOTES:

1. Metallized castellations shall be connected to plane 1 terminals

and extend toward plane 2 across at least two layers of ceramic

or completely across all of the ceramic layers to make electrical

connection with the optional plane 2 terminals.

2. Unless otherwise specified, a minimum clearance of 0.015 inch

(0.38mm) shall be maintained between all metallized features

(e.g., lid, castellations, terminals, thermal pads, etc.)

3. Symbol “N” is the maximum number of terminals. Symbols “ND”

and “NE” are the number of terminals along the sides of length

“D” and “E”, respectively.

4. The required plane 1 terminals and optional plane 2 terminals (if

used) shall be electrically connected.

5. The corner shape (square, notch, radius, etc.) may vary at the

manufacturer’s option, from that shown on the drawing.

6. Chip carriers shall be constructed of a minimum of two ceramic

layers.

7. Dimension “A” controls the overall package thickness. The maxi-

mum “A” dimension is package height before being solder dipped.

8. Dimensioning and tolerancing per ANSI Y14.5M-1982.

9. Controlling dimension: INCH.

相关PDF资料 |

PDF描述 |

|---|---|

| HSP43124SC-45Z | IC I/O FILTER SER 24BIT 28-SOIC |

| HSP43168JC-33Z | IC FIR FILTER DUAL 84-PLCC |

| HSP43216JC-52Z | IC HALFBAND FILTER 84-PLCC |

| HSP43220JC-33Z | IC DECIMATING DGTL FILTER 84PLCC |

| IA188EM-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HS1-3182-9+ | 功能描述:接口 - 专用 ARINC BUS INTERFACE LINE DRVR-40+85C RoHS:否 制造商:Texas Instruments 产品类型:1080p60 Image Sensor Receiver 工作电源电压:1.8 V 电源电流:89 mA 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:BGA-59 |

| HS1-3182B4076-001 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HS1-3282-2R | 制造商:Harris Corporation 功能描述: |

| HS1-3282-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HS1-3282-8 | 制造商:Intersil Corporation 功能描述:CMOS ARINC BUS INTERFACE CIRCUIT 制造商:Intersil Corporation 功能描述:CMOS BUS INTRFC CIRCUIT 40CDIP - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。