- 您现在的位置:买卖IC网 > PDF目录370740 > HY5DV281622AT 8Mx16|3.3V|4K|45|DDR SDRAM - 128M PDF资料下载

参数资料

| 型号: | HY5DV281622AT |

| 英文描述: | 8Mx16|3.3V|4K|45|DDR SDRAM - 128M |

| 中文描述: | 8M × 16位| 3.3 | 4K的| 45 | DDR SDRAM内存- 128M的 |

| 文件页数: | 7/27页 |

| 文件大小: | 273K |

| 代理商: | HY5DV281622AT |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

Rev. 0.3/May. 02

7

HY5DV281622AT

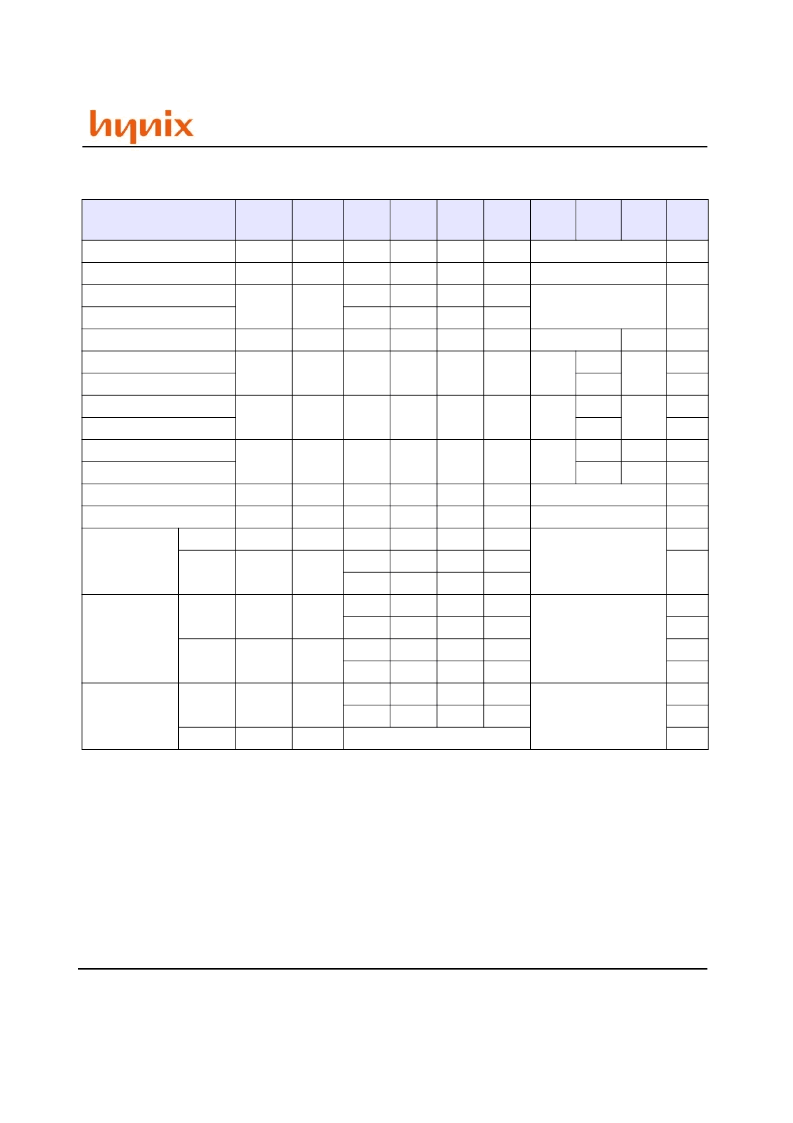

SIMPLIFIED COMMAND TRUTH TABLE

Command

CKEn-1

CKEn

CS

RAS

CAS

WE

ADDR

A10/

AP

BA

Note

Extended Mode Register Set

H

X

L

L

L

L

OP code

1,2

Mode Register Set

H

X

L

L

L

L

OP code

1,2

Device Deselect

H

X

H

X

X

X

X

1

No Operation

L

H

H

H

Bank Active

H

X

L

L

H

H

RA

V

1

Read

H

X

L

H

L

H

CA

L

V

1

Read with Autoprecharge

H

1,3

Write

H

X

L

H

L

L

CA

L

V

1

Write with Autoprecharge

H

1,4

Precharge All Banks

H

X

L

L

H

L

X

H

X

1,5

Precharge selected Bank

L

V

1

Read Burst Stop

H

X

L

H

H

L

X

1

Auto Refresh

H

H

L

L

L

H

X

1

Self Refresh

Entry

H

L

L

L

L

H

X

1

Exit

L

H

H

X

X

X

1

L

H

H

H

Precharge Power

Down Mode

Entry

H

L

H

X

X

X

X

1

L

H

H

H

1

Exit

L

H

H

X

X

X

1

L

H

H

H

1

Active Power

Down Mode

Entry

H

L

H

X

X

X

X

1

L

V

V

V

1

Exit

L

H

X

1

Note :

1. LDM/UDM states are Don’t Care. Refer to below Write Mask Truth Table.

2. OP Code(Operand Code) consists of A0~A11 and BA0~BA1 used for Mode Register setting during Extended MRS or MRS.

Before entering Mode Register Set mode, all banks must be in a precharge state and MRS command can be issued after tRP

period from Prechagre command.

3. If a Read with Autoprecharge command is detected by memory component in CK(n), then there will be no command presented

to activated bank until CK(n+BL/2+tRP).

4. If a Write with Autoprecharge command is detected by memory component in CK(n), then there will be no command presented

to activated bank until CK(n+BL/2+1+tDPL+tRP). Last Data-In to Prechage delay(tDPL) which is also called Write Recovery Time

(tWR) is needed to guarantee that the last data has been completely written.

5. If A10/AP is High when Precharge command being issued, BA0/BA1 are ignored and all banks are selected to be

precharged.

( H=Logic High Level, L=Logic Low Level, X=Don’t Care, V=Valid Data Input, OP Code=Operand Code, NOP=No Operation )

相关PDF资料 |

PDF描述 |

|---|---|

| HY5DV281622AT-5 | SDRAM|DDR|4X2MX16|CMOS|TSSOP|66PIN|PLASTIC |

| HY5DV651622TC-G55 | DDR Synchronous DRAM |

| HY5DV651622TC-G6 | DDR Synchronous DRAM |

| HY5DV651622TC-G7 | DDR Synchronous DRAM |

| HY5DV651622T-G55 | DDR Synchronous DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HY5DV281622AT-5 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SDRAM|DDR|4X2MX16|CMOS|TSSOP|66PIN|PLASTIC |

| HY5DV281622DT | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:128M(8Mx16) GDDR SDRAM |

| HY5DV281622DT-33 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:128M(8Mx16) GDDR SDRAM |

| HY5DV281622DT-36 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:128M(8Mx16) GDDR SDRAM |

| HY5DV281622DT-4 | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:128M(8Mx16) GDDR SDRAM |

发布紧急采购,3分钟左右您将得到回复。