- 您现在的位置:买卖IC网 > PDF目录378599 > IA88C00-PDW48C (Innovasic Semiconductor) Microcontroller PDF资料下载

参数资料

| 型号: | IA88C00-PDW48C |

| 厂商: | Innovasic Semiconductor |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件页数: | 25/80页 |

| 文件大小: | 707K |

| 代理商: | IA88C00-PDW48C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

IA88C00

Microcontroller

Data Sheet

As of Production Version -01

Copyright

2005 ENG 21 0 050519-00 www.Innovasic

Innovasic.com

Innovasic Semiconductor

Page 25 of 80 1.888.824.4184

When an interrupt in one of the 8 levels occurs and the corresponding mask bit is not set, the level bit of

the interrupt is set to 1. The interrupt structure contains 8 levels of interrupt, 16 vectors and 27 sources.

Interrupt priority is assigned by level and controlled by the Interrupt Priority Register (IPR)

ControlRegR255B0. Each level is masked (or enabled) according to the bits in the Interrupt Mask

Register (IMR) SystemRegR221. Each bit of the Interrupt Mask register corresponds to one of the 8

levels of interrupts, IRQ register (SystemRegR220). When the corresponding bit in the Interrupt Mask

register is set to one, that level interrupt is disabled.

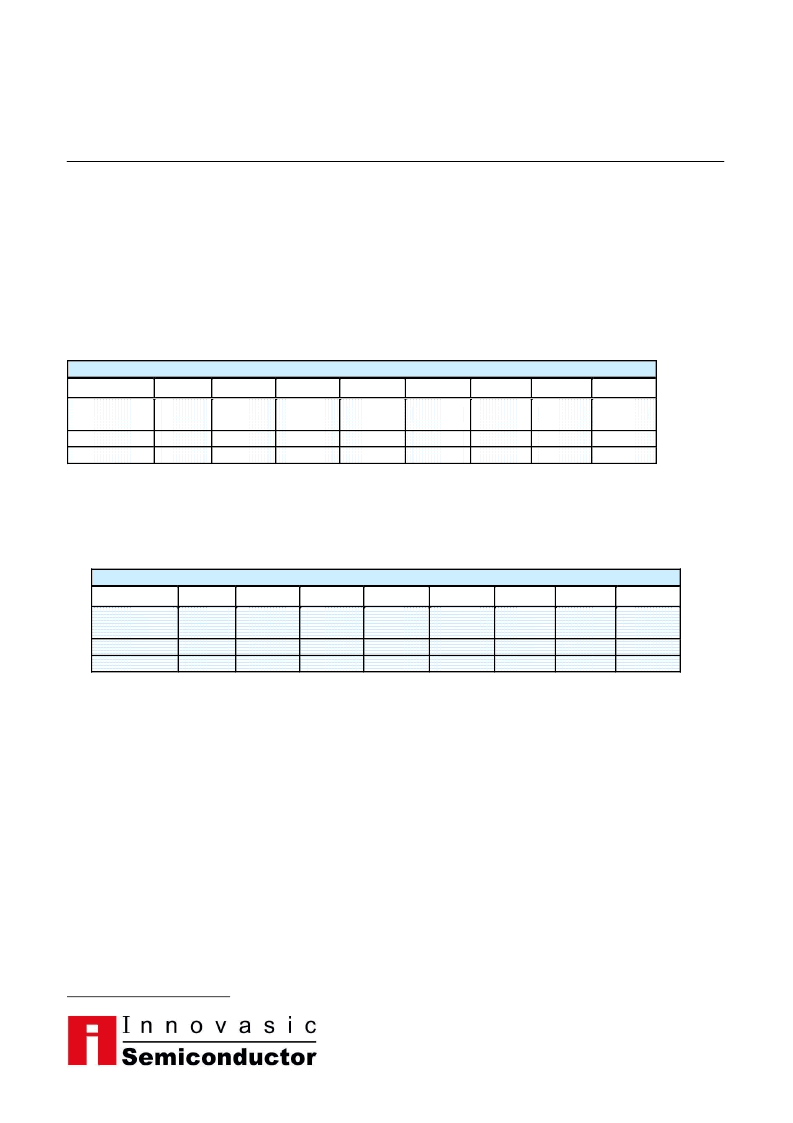

Figure 18. System Mode Register (SYM), R222

Bit

7

Not

Used

R/W

6

Not

Used

R/W

5

Not

Used

R/W

4

3

2

1

0

FIS2

FSI1

FSI0

FSE

GIE

Initial Value

Read/Write

The Fast Interrupt Select (FSI) selects which level interrupt can be treated as a fast interrupt. Fast

Interrupt Enable (FSE), when set to 1, enables the selected level for fast interrupt. Global Interrupt Enable

(GIE), when set to 1, enables interrupts in general.

R/W

R/W

R/W

R/W

R/W

Figure 19. Halt Mode Register (HMR), R223

Bit

7

Not

Used

R/W

6

Not

Used

R/W

5

Not

Used

R/W

4

Not

Used

R/W

3

2

1

0

D3

D2

D1

D0

Initial Value

Read/Write

D3 - CPU HALT mode

- Writing a zero to this bit will invoke the HALT mode upon the execution of the

WFI instruction. The UART and counters can be halted only if D3 is 0. During HALT the internal CPU

clock is disabled, and no address strobe is generated. A hardware reset sets this bit to a 1.

1

1

1

1

R/W

R/W

R/W

R/W

D2 - Disable UART

- Writing a zero to the bit will disable the UART. No interrupt request will be

generated. A 1 will make the UART and its interrupt logic remain active in HALT mode. A hardware

reset forces this bit to a 1.

D1 - Disable CT1

- Similar to CT0. When the counters are cascaded, the HALT mode 32-bit counter is

determined by the logical state of D1. A hardware reset forces this bit to a 1.

D0 - Disable CT0

- Writing a zero to this bit will disable the CT0 in HALT mode. No interrupt request

will be generated in this case. A 1 will keep the CT0 active. A hardware reset forces this bit to a 1.

相关PDF资料 |

PDF描述 |

|---|---|

| IA88C00-PDW48C-R | Microcontroller |

| IA88C00-PDW48I | Microcontroller |

| IA88C00-PDW48I-R | Microcontroller |

| IA88C00-PLC68C | Microcontroller |

| IA88C00-PLC68C-R | Microcontroller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IA88C00-PDW48C-R | 制造商:INNOVASIC 制造商全称:INNOVASIC 功能描述:Microcontroller |

| IA88C00-PDW48I | 制造商:INNOVASIC 制造商全称:INNOVASIC 功能描述:Microcontroller |

| IA88C00-PDW48I-R | 制造商:INNOVASIC 制造商全称:INNOVASIC 功能描述:Microcontroller |

| IA88C00-PLC68C | 制造商:INNOVASIC 制造商全称:INNOVASIC 功能描述:Microcontroller |

| IA88C00-PLC68C-R | 制造商:INNOVASIC 制造商全称:INNOVASIC 功能描述:Microcontroller |

发布紧急采购,3分钟左右您将得到回复。