- 您现在的位置:买卖IC网 > PDF目录296203 > IC42S81600L-6TI 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM PDF资料下载

参数资料

| 型号: | IC42S81600L-6TI |

| 英文描述: | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| 中文描述: | 4(2)M中的x 8(16)位× 4银行(128 - Mbit的)同步动态RAM |

| 文件页数: | 14/69页 |

| 文件大小: | 1118K |

| 代理商: | IC42S81600L-6TI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

IC42S81600/IC42S81600L

IC42S16800/IC42S16800L

Integrated Circuit Solution Inc.

21

DR023-0E 6/11/2004

Auto Precharge

During a read or write command cycle, A10 controls whether auto precharge is selected. If A10 is high in the read or write

command (Read with Auto precharge command or Write with Auto precharge command), auto precharge is selected and

begins automatically.

In the write cycle, tDAL(min.) must be satisfied before asserting the next activate command to the bank being precharged.

When using auto precharge in the read cycle, knowing when the precharge starts is important because the next activate

command to the bank being precharged cannot be executed until the precharge cycle ends. Once auto precharge has

started, an activate command to the bank can be asserted after tRP has been satisfied.

A Read or Write command without auto - precharge can be terminated in the midst of a burst operation. However, a Read

or Write command with auto - precharge can not be interrupted by the same bank commands before the entire burst opera-

tion is completed. Therefore use of the same bank Read, Write, Precharge or Burst Stop command is prohibited during

a read or write cycle with auto - precharge. It should be noted that the device will not respond to the Auto - Precharge com-

mand if the device is programmed for full page burst read or write cycles.

The timing when the auto precharge cycle begins depends both on both the CAS Iatency programmed into the mode reg-

ister and whether the cycle is read or write.

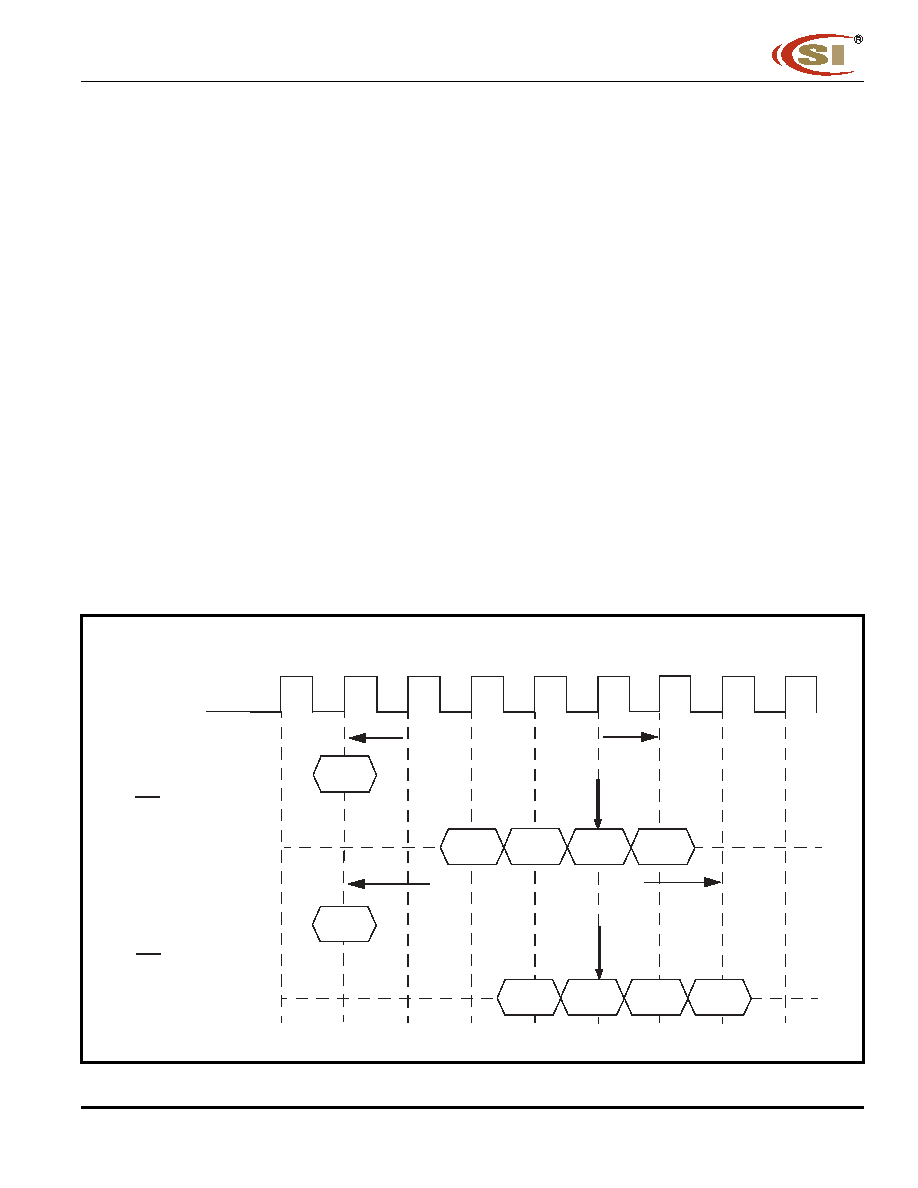

Read with Auto Precharge

During a READA cycle, the auto precharge begins one clock earlier (CL = 2) or two clocks earlier (CL = 3) than the last word

output.

READ with AUTO PRECHARGE

Burst lengh = 4

CLK

Command

CAS

latency = 2

DQ

Command

CAS

latency = 3

DQ

Remark READA means READ with AUTO PRECHARGE

Hi - Z

Auto precharge starts

QB0

QB3

QB2

QB1

READA B

T0

T1

T2

T3

T4

T5

T6

T7

Auto precharge starts

Hi - Z

T8

QB0

QB3

QB2

QB1

No New Command to Bank B

相关PDF资料 |

PDF描述 |

|---|---|

| IC42S81600L-6TIG | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-7T | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-7TG | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-7TI | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-8T | 4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IC42S81600L-6TI(G) | 制造商:ICSI 制造商全称:Integrated Circuit Solution Inc 功能描述:4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-6TIG | 制造商:ICSI 制造商全称:Integrated Circuit Solution Inc 功能描述:4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-7T | 制造商:ICSI 制造商全称:Integrated Circuit Solution Inc 功能描述:4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-7T(G) | 制造商:ICSI 制造商全称:Integrated Circuit Solution Inc 功能描述:4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IC42S81600L-7TG | 制造商:ICSI 制造商全称:Integrated Circuit Solution Inc 功能描述:4(2)M x 8(16) Bits x 4 Banks (128-MBIT) SYNCHRONOUS DYNAMIC RAM |

发布紧急采购,3分钟左右您将得到回复。