- 您现在的位置:买卖IC网 > PDF目录67684 > ICS1522MLF 230 MHz, VIDEO CLOCK GENERATOR, PDSO24 PDF资料下载

参数资料

| 型号: | ICS1522MLF |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 230 MHz, VIDEO CLOCK GENERATOR, PDSO24 |

| 封装: | SOIC-24 |

| 文件页数: | 4/13页 |

| 文件大小: | 2240K |

| 代理商: | ICS1522MLF |

12

ICS1522

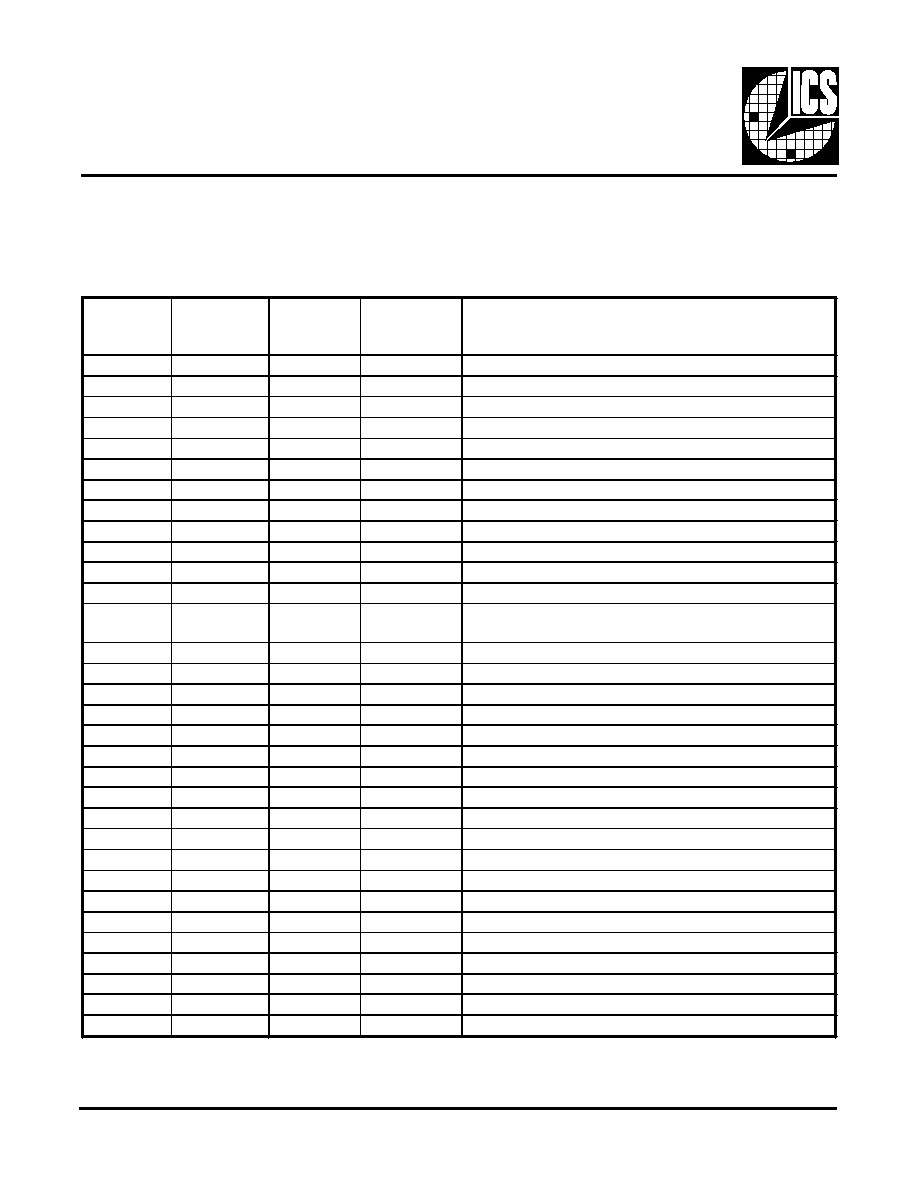

Memory Definition

ICS1522 memory is loaded serially with the least significant bit clocked into the device first. After the R/Wn bit, the next

three bits of the programming word (15 bits) hold the memory location to be loaded. The least significant 11 bits are the

data to be loaded (see Timing Diagram).

MEMORY

ADDRESS

DATA BITS

DEFAULT

VALUES

(HEX)

NAME

DESCRIPTION

000

0-10

04F

F(0:10)

Feedback Divider Modulus (Modulus = Value +1)

001

0-7

03

LO(0:7)

M Counter Lo Sync State

001

8-10

0

A

Don't Care

010

0-7

06

HI(0:7)

M Counter Hi Sync State

010

8-10

0

A

Don't Care

011

0-9

013

R(0:9)

Reference Divider Modulus (Modulus = Value + 1)

011

10

0

REF

POL External Reference Polarity (1 =Invert)

100

0-2

4

VCO(0:2)

VCO Gain

100

3-5

3

PFD(0:2)

Phase Detector Gain

100

6

1

PDEN

Phase Detector Enable (1 =Enable)

100

7

1

INT_FLT

Internal Loop Filter (1 = Internal)

100

8

1

INT_VCO

Internal VCO (1 = Internal)

100

9

0

CLK_SEL

Internal feedback input clock select

(0 = VCO Output)

100

10

1

Reserved

Reserved - Set to One

101

0

1

FBK_SEL

Feedback Select (1 =Internal)

101

1

0

FBK_POL

External Feedback Polarity (1 =Invert)

101

2

0

ADD

Addition of 1 VCO Cycle (0 to 1 = Add)

101

3

0

SWLW

Removal of 1 VCO Cycle (0 to 1 = Swallow)

101

4-5

0

PDA(0:1)

Output Post-Scaler

101

6-7

3

PDB(0:1)

Feedback Post-Scaler

101

8

1

LD_LG

Fine Phase Adj. Lead/Lag (1=Lead)

101

9

0

F_EN

Fine Phase Adj. Enable (1=Enable)

101

10

1

Reserved

Reserved - Set to One

110

0-2

7

L(0:2)

Load Counter

110

3

0

OMUX1

OUT1 Select (0 = Load Cntr, 1 = Div By 4 0Deg)

110

4

0

OMUX2

OUT2 Select (0 = Int Fbk, 1 = Div By 4 90Deg)

110

5

0

OMUX3

OUT3 Select (0 = Sync Lo, 1 = Div By 4 180Deg)

110

6

1

OMUX4

OUT4 Select (0 = Sync Hi, 1 = Div By 4 270Deg)

110

7

0

DACRST

Output Reset (CLK+ = 1, CLK- = 0)

110

8

0

AUXEN

Output Test Mode (1 = Test, See Board Test Support)

110

9

0

AUXCLK

Output Clock When in Test Mode

110

10

0

EXTREF

XTAL/EXTREF Input Buffer (1=EXTREF)

相关PDF资料 |

PDF描述 |

|---|---|

| ICS1524AMT | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS1524AM | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS1524AMT | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS1527G-60LFTR | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS1562BM-001LF | 260 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1523 | 制造商:ICS 制造商全称:ICS 功能描述:High-Performance Programmable Line-Locked Clock Generator |

| ICS1523M | 功能描述:IC VIDEO CLK SYNTHESIZER 24-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1523MLF | 功能描述:IC SYNTHESIZER VIDEO CLK 24-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ICS1523MLFT | 功能描述:IC VIDEO CLK SYNTHESIZER 24-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS1523MT | 功能描述:IC VIDEO CLK SYNTHESIZER 24-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。