- 您现在的位置:买卖IC网 > PDF目录67684 > ICS1524AM (INTEGRATED DEVICE TECHNOLOGY INC) 250 MHz, OTHER CLOCK GENERATOR, PDSO24 PDF资料下载

参数资料

| 型号: | ICS1524AM |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| 封装: | 0.300INCH, SOIC-24 |

| 文件页数: | 23/24页 |

| 文件大小: | 354K |

| 代理商: | ICS1524AM |

ICS1524A

8

ICS1524A Rev D 12/23/2005

Name:

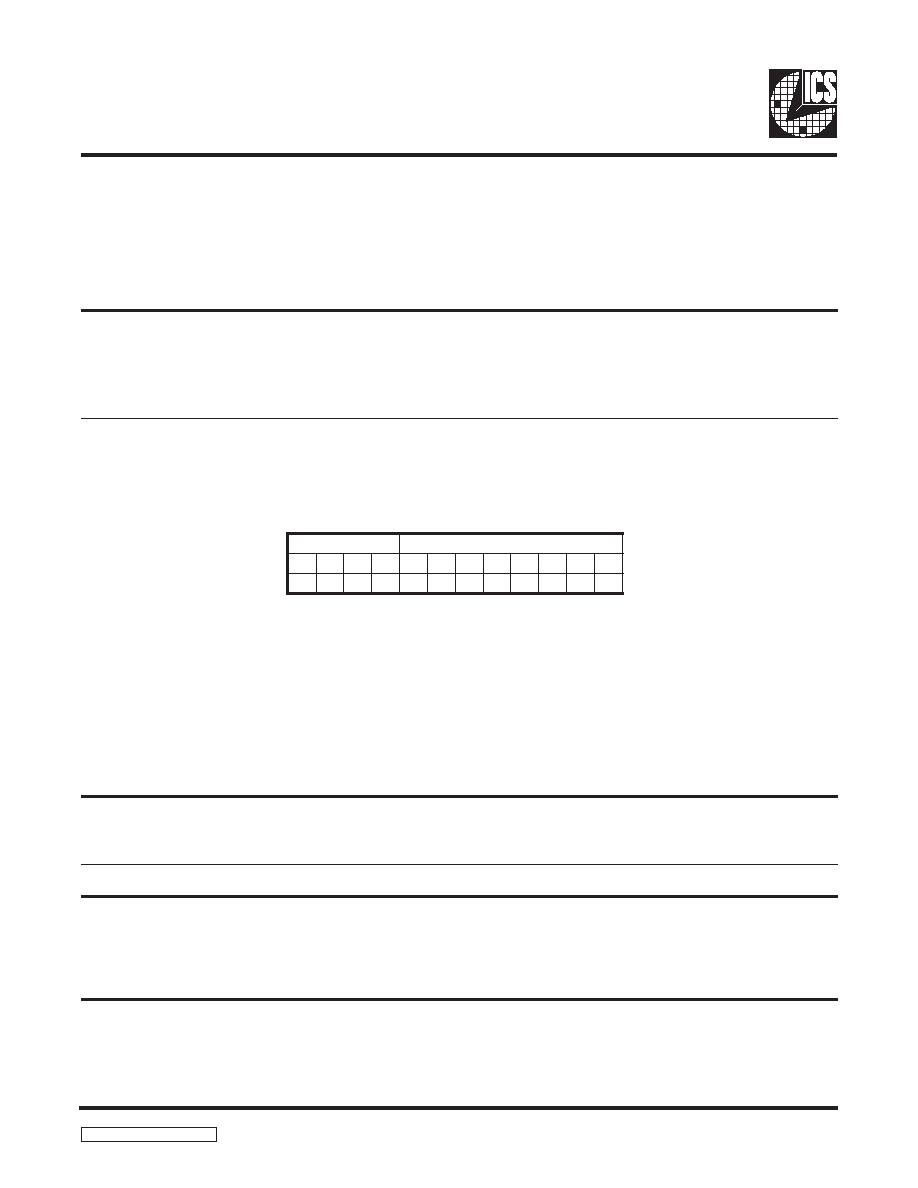

Feedback Divider 0 Register / Feedback Divider 1 Register

Register:

2h, 3h

Index:

Read / Write*

Bit Name

Index

Bit #

Reset Value

Description

FBD 0-7

2

0 -7

FF

PLL Feedback Divider LSBs (0 -7).* When Bit 0 = 0, then the total

number of clocks per line is even. When Bit 0 = 1, then the total

number of clocks is odd.

FBD 8 -11

3

0 -3

F

PLL Feedback Divider MSBs (8 -11)*

Reserved

3

4 -7

Reserved

Feedback Divider Modulus

=

*Double-buffered registers. Actual working registers are loaded during software PLL reset.

See Register 8h for details.

Name:

DPA Offset Register

Register:

4h

Index:

Read / Write

Bit Name

Bit #

Reset Value

Description

DPA_OS0-5

0 - 5

0

Dynamic Phase Adjust Offset

Reserved

6

0

Reserved

Fil_Sel

7

0

Loop Filter Select

Bit

Name

Description

0-5

DPA_OS0-5

Dynamic Phase Adjust Offset.

Selects clock edge offset in discrete steps from zero to one clock period minus one step.

Resolution (number of delay elements per clock cycle) is selected by DPA_Res0-1 (Reg 5:0-1).

Note: Offsets equal to or greater than one clock period are neither recommended nor supported.

Example: For DPA_Res0-1=01H, the clock can be delayed from 0 to 31 steps.

7

Fil_Sel

Selects external loop filter (0) or internal loop filter (1).

The use of an external loop filter is strongly recommended for all designs. Typical loop filter

values are 6.8K Ohms for the series resistor, 3300 pF RF-type capacitor for the series capacitor,

and 33 pF for the shunt capacitor.

12

≤ Feedback Divider Modulus ≤ 4103

The value that is programmed into these two registers, plus a value of 8, defines the total number of clock periods that the ICS

1524 generates between HSYNCs. Program these registers with the total number of horizontal clocks per line minus 8.

3

g

e

R2

g

e

R

32

1

0

7

65

4

32

1

0

+8

相关PDF资料 |

PDF描述 |

|---|---|

| ICS1524AMT | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS1527G-60LFTR | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS1562BM-001LF | 260 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS1567M-XXX-LF | 180 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS1574BM | 130 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1524AMLF | 功能描述:IC CLK GEN SSTL_3/PECL 24-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1524AMLFT | 功能描述:IC CLK GEN SSTL_3/PECL 24-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1524AMT | 功能描述:IC CLK GEN SSTL_3/PECL 24-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1524M | 制造商:ICS 制造商全称:ICS 功能描述:Dual Output Phase Controlled SSTL-3/PECL Clock Generator |

| ICS1524MT | 制造商:ICS 制造商全称:ICS 功能描述:Dual Output Phase Controlled SSTL-3/PECL Clock Generator |

发布紧急采购,3分钟左右您将得到回复。