- 您现在的位置:买卖IC网 > PDF目录67684 > ICS1524AMT 250 MHz, OTHER CLOCK GENERATOR, PDSO24 PDF资料下载

参数资料

| 型号: | ICS1524AMT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| 封装: | 0.300INCH, SOIC-24 |

| 文件页数: | 8/24页 |

| 文件大小: | 354K |

| 代理商: | ICS1524AMT |

ICS1524A

16

ICS1524A Rev D 12/23/2005

PECL Outputs

For information on using the ICS1524A’s PECL output pins, please refer to Application Note 4: Designing a Custom

PECL Interface for the ICS1523

SSTL_3 Outputs

Unterminated Outputs

In the ICS1524A, unterminated SSTL_3 output pins display exponential transitions similar to those of rectangular

pulses presented to RC loads. The 10-90% rise time is typically 1.6 ns, and the corresponding fall time is typically

700 ps. In turn, this asymmetry contributes to duty cycle asymmetry at higher output frequencies. In the absence of

significant load capacitance (which can further increase rise and fall time), this asymmetry is the dominant factor

determining high-frequency performance of these single-ended outputs. Typically, no termination is required either for

the LOCK/REF, FUNC, and CLK/2 outputs or for CLK outputs up to approximately 135 MHz.

Terminated Outputs

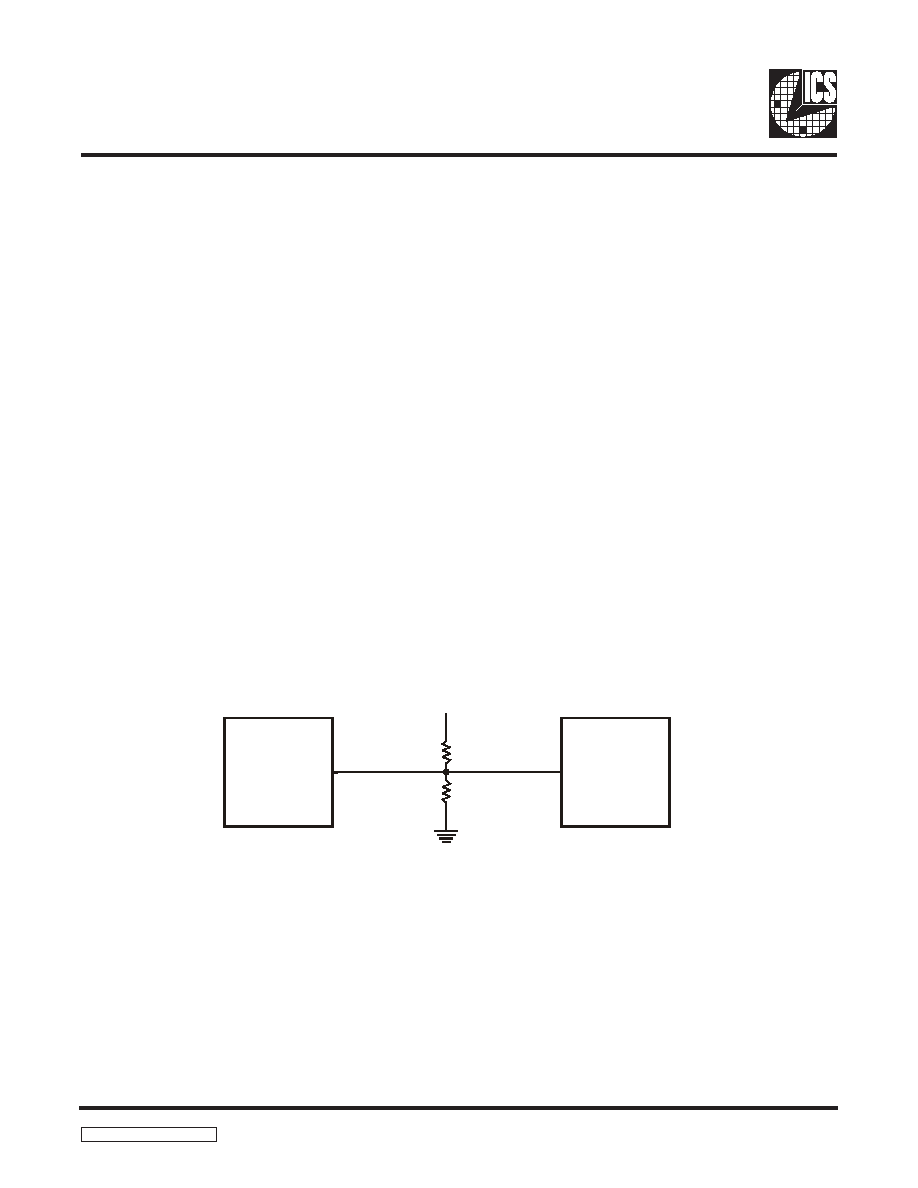

SSTL_3 outputs are intended to terminate in low impedances to reduce the effect of external circuit capacitance.

Use of transmission line techniques enables use of longer traces between source and driver without increasing

ringing due to reflections. Where external capacitance is minimal and substantial voltage swing is required to meet

LVTTL VIH and VOL requirements, the intrinsic rise and fall times of ICS1524A SSTL outputs are only slightly improved

by termination in a low impedance.

The ICS1524A SSTL output source impedance is typically less than 60 Ohms. Termination impedance of 100 Ohms

reduces output swing by less than 30% which is more than enough to drive a single load of LVTTL inputs.

For more information on using the ICS1524A’s SSTL output pins, please refer to Application Note 3: Using SSTL_3

Outputs with CMOS or LVTTL Inputs

ICS1524A

VDD

SSTL-3 Output

330

150

Single

LVTTL

Load

相关PDF资料 |

PDF描述 |

|---|---|

| ICS1527G-60LFTR | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS1562BM-001LF | 260 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS1567M-XXX-LF | 180 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS1574BM | 130 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS1890Y-14 | 1 CHANNEL(S), 100M bps, SERIAL COMM CONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1524M | 制造商:ICS 制造商全称:ICS 功能描述:Dual Output Phase Controlled SSTL-3/PECL Clock Generator |

| ICS1524MT | 制造商:ICS 制造商全称:ICS 功能描述:Dual Output Phase Controlled SSTL-3/PECL Clock Generator |

| ICS1526 | 制造商:ICS 制造商全称:ICS 功能描述:Video Clock Synthesizer |

| ICS1526G | 功能描述:IC VIDEO CLK SYNTHESIZER 16TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1526GILF | 功能描述:IC VIDEO CLK SYNTHESIZER 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。