- 您现在的位置:买卖IC网 > PDF目录8981 > ICS1562BM-001T (IDT, Integrated Device Technology Inc)IC VIDEO CLK SYNTHESIZER 16-SOIC PDF资料下载

参数资料

| 型号: | ICS1562BM-001T |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 14/20页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO CLK SYNTHESIZER 16-SOIC |

| 标准包装: | 2,500 |

| 类型: | 时钟/频率合成器,时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,TTL,晶体 |

| 输出: | CMOS,PECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 260MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

| 其它名称: | 1562BM-001T |

Digital Inputs - ICS1562B-201 Option

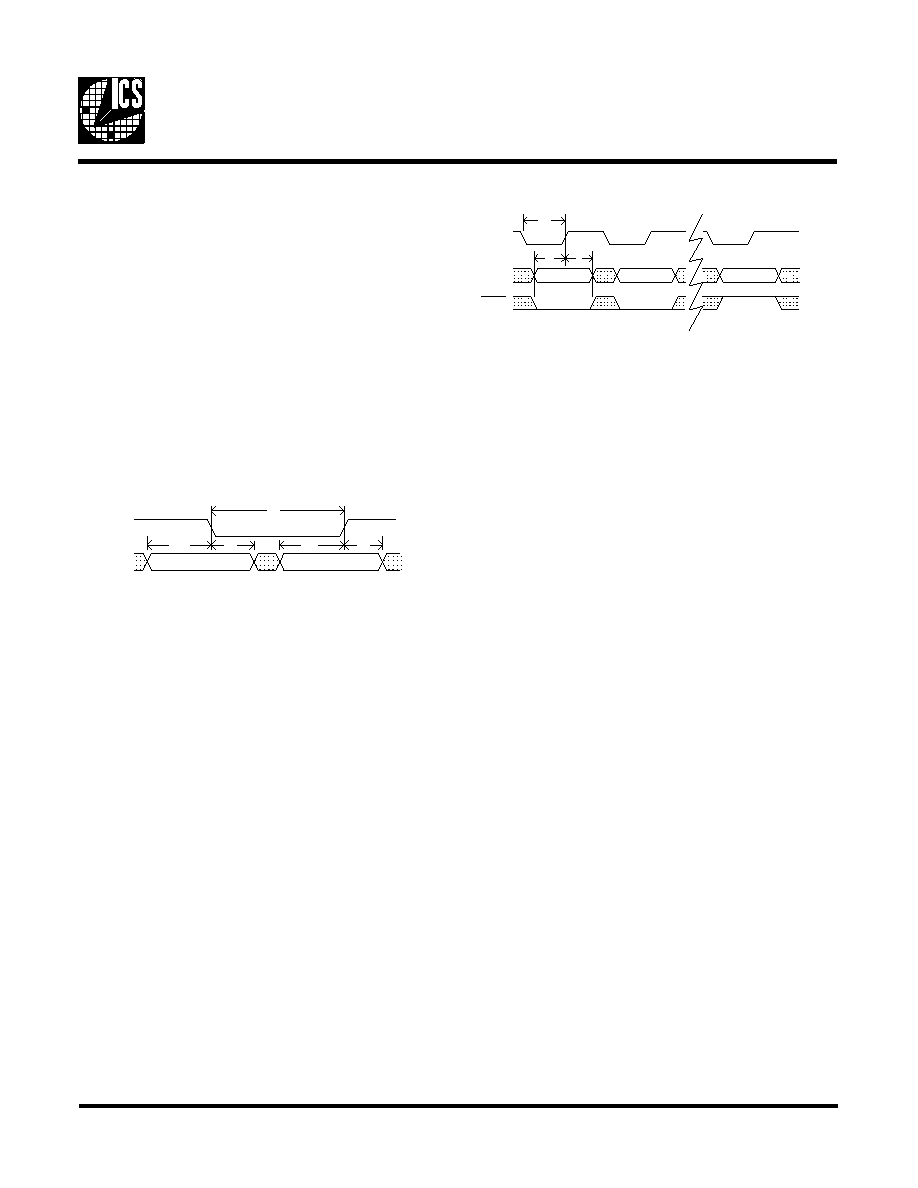

The programming of the ICS1562B-201 is performed serially

by using the DATCLK, DATA, and HOLD~pins to load an

internal shift register.

DATA is shifted into the register on the rising edge of

DATCLK. The logic value on the HOLD~pin is latched at the

same time. When HOLD~ is low, the shift register may be

loaded without disturbing the operation of the ICS1562B.

When high, the shift register outputs are transferred to the

control registers, and the new programming information be-

comes active. Ordinarily, a high level should be placed on the

HOLD~ pin when the last data bit is presented. See Figure 3

for the programming sequence.

An additional control pin on the ICS1562B-201, BLANK can

perform either of two functions. It may be used to disable the

phase-frequency detector in line-locked applications. Alterna-

tively, the BLANK pin may be used as a synchronous enable

for VRAM shift clock generation. See sections on Line-Locked

Operations and VRAM shift clock generation for details.

Output Description

The differential output drivers, CLK+ and CLK, are current-

mode and are designed to drive resistive terminations in a

complementary fashion. The outputs are current-sinking only,

with the amount of sink current programmable via the IPRG

pin. The sink current, which is steered to either CLK+or CLK-,

is four times the current supplied to the IPRG pin. For most

applications, a resistor from VDDO to IPRG will set the current

to the necessary precision. Additionally, minor adjustment to

the duty factor can be achieved under register control.

The LOAD output is a high-current CMOS type drive whose

frequency is controlled by a programmable divider that may be

selected for a modulus of 3, 4, 5, 6, 8, 10, 12, 16 or 20. It may

also be suppressed under register control. The load output may

be programmed to output the VCO frequency divided by 2 (see

AUX_N1 description in Register Mapping section), inde-

pendent of the differential output and N1 divider modulus.

The LD/N2 output is high-current CMOS type drive whose

frequency is derived from the LOAD output. The programma-

ble modulus may range from 1 to 512 in steps of one.

5

4

2

1

3

DATA VALID

ADDRESS VALID

AD0-AD3

STROBE

ICS1562B-001 Register Loading

Figure 2

8

67

DATCLK

DATA

HOLD

DATA_1

DATA_2

DATA_56

ICS1562B-201 Register Loading

Figure 3

This allows the synthesizer to be completely programmed for

the desired frequency before it is made active. Once the part

has been “unlocked” by the 32 writes, programming becomes

effective immediately.

ALL registers identified in the data sheet (0-9, 11, 12 & 15)

MUST be written upon initial programming. The programming

registers are not initialized upon power-up, but the latched

outputs of those registers are. The latch is made transparent

after 32 register writes. If any register has not been written, the

state upon power-up (random) will become effective. Registers

13 & 14 physically do not exist. Register 10 does exist, but is

reserved for future expansion. To insure compatibility with

possible future modifications to the database, ICS recommends

that all three unused locations be written with zero.

ICS1562B

3

相关PDF资料 |

PDF描述 |

|---|---|

| AD5062BRJZ-2500RL7 | IC DAC 16BIT 2.7-5.5V SOT23-8 |

| ICS843023AGILFT | IC CLK GENERATOR LVPECL 8-TSSOP |

| AD5063BRMZ | IC DAC 16BIT 2.7-5.5V 10-MSOP |

| AD5063BRMZ-1 | IC DAC 16BIT 2.7-5.5V 10MSOP |

| VE-J0P-MZ-F4 | CONVERTER MOD DC/DC 13.8V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1562BM-201 | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1562BM-201-4 | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1562BM-201-4LF | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| ICS1562BM-201-4LFT | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| ICS1562BM-201LF | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。