- 您现在的位置:买卖IC网 > PDF目录8981 > ICS1562BM-001T (IDT, Integrated Device Technology Inc)IC VIDEO CLK SYNTHESIZER 16-SOIC PDF资料下载

参数资料

| 型号: | ICS1562BM-001T |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 15/20页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO CLK SYNTHESIZER 16-SOIC |

| 标准包装: | 2,500 |

| 类型: | 时钟/频率合成器,时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,TTL,晶体 |

| 输出: | CMOS,PECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 260MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

| 其它名称: | 1562BM-001T |

Pipeline Delay Reset Function

The ICS1562B implements the clocking sequence required to

reset the pipeline delay on Brooktree RAMDACs when the

LOAD output is programmed for a modulus of either 3, 4, 5,

6, 8 or 10. This sequence can be generated by setting the

appropriate register bit (DACRST) to a logic 1 and then reset-

ting to logic 0.

When changing frequencies, it is advisable to allow 500 mi-

croseconds after the new frequency is selected to activate the

reset function. The output frequency of the synthesizer should

be stable enough at that point for the video DAC to correctly

execute its reset sequence. See Figure 4 for a diagram of the

pipeline delay reset sequence.

Reference Oscillator and Crystal

Selection

The ICS1562B has circuitry on-board to implement a Pierce

oscillator with the addition of only one external component, a

quartz crystal. Pierce oscillators operate the crystal in anti-

(also called parallel-) resonant mode. See the AC Charac-

teristics for the effective capacitive loading to specify when

ordering crystals.

Series-resonant crystals may also be used with the ICS1562B.

Be aware that the oscillation frequency will be slightly higher

than the frequency that is stamped on the can (typically 0.025-

0.05%).

As the entire operation of the phase-locked loop depends on

having a stable reference frequency, we recommend that the

crystal be mounted as closely as possible to the package. Avoid

routing digital signals or the ICS1562B outputs underneath or

near these traces. It is also desirable to ground the crystal can

to the ground plane, if possible.

If an external reference frequency source is to be used with the

ICS1562B. it is important that it be jitter-free. The rising and

falling edges of that signal should be fast and free of noise for

best results.

The loop phase is locked to the falling edges of the XTAL1

input signals if the REFPOL bit is set to logic 0.

Internal Feedback

The ICS1562B supports LOAD (N1) and N2 divider

chains to act as the feedback divider for the PLL.

The N1 and N2 divider chains allow a much larger modulus to

be achieved than the PLL’s own feedback divider. Additionally,

the output of the N2 counter is accessible off-chip for perform-

ing horizontal reset of the graphics system, where necessary.

This mode is set under register control (ALTLOOP bit). The

reference divider (R counter) will ordinarily be set to divide by

1 in this mode, and the reference input will be supplied to

the XTAL1 input. The output frequency of the synthesizer

will then be:

F(CLK) : = F (XTAL1) . N1 . N2.

By using the phase-detector hardware disable mode, the PLL

can be made to free-run at the beginning of the vertical interval

of the external video, and can be reactivated at its completion.

ICS1562B-001 The ICS1562B-001 supports phase detector

disable via a special control mode. When the

PDRSTEN (phase detector reset enable) bit is

set and the last address latched is 15 (0Fh), a

high level on AD3 will disable PLL locking.

ICS1562B-201 The ICS1562B-201 supports phase detector

disable via the BLANK pin. When the

PDRSTEN bit is set, a high level on the

BLANK input will disable PLL locking.

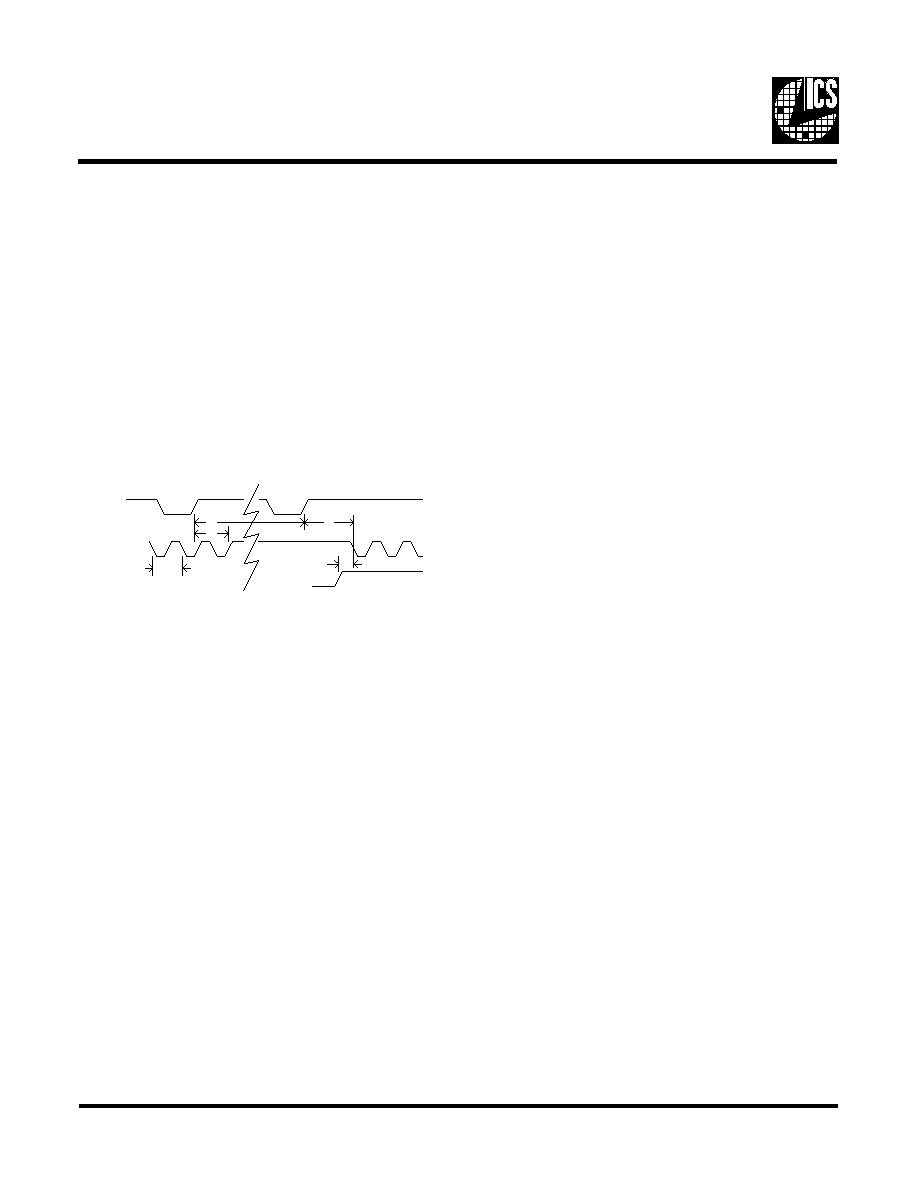

Pipeline Delay Reset Timing

STROBE

or

DATCLK

CLK+

LOAD

10

9

11

12

TCLK

Figure 4

ICS1562B

4

相关PDF资料 |

PDF描述 |

|---|---|

| AD5062BRJZ-2500RL7 | IC DAC 16BIT 2.7-5.5V SOT23-8 |

| ICS843023AGILFT | IC CLK GENERATOR LVPECL 8-TSSOP |

| AD5063BRMZ | IC DAC 16BIT 2.7-5.5V 10-MSOP |

| AD5063BRMZ-1 | IC DAC 16BIT 2.7-5.5V 10MSOP |

| VE-J0P-MZ-F4 | CONVERTER MOD DC/DC 13.8V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1562BM-201 | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1562BM-201-4 | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS1562BM-201-4LF | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| ICS1562BM-201-4LFT | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| ICS1562BM-201LF | 功能描述:IC VIDEO CLK SYNTHESIZER 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。