- 您现在的位置:买卖IC网 > PDF目录10591 > ICS2008BVLFT (IDT, Integrated Device Technology Inc)IC TIME CODE RCVR/GEN 44-PLCC PDF资料下载

参数资料

| 型号: | ICS2008BVLFT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 21/22页 |

| 文件大小: | 0K |

| 描述: | IC TIME CODE RCVR/GEN 44-PLCC |

| 标准包装: | 500 |

| 类型: | SMPTE 时间代码接收器,发生器 |

| 应用: | 多媒体 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC(16.59x16.59) |

| 包装: | 带卷 (TR) |

| 其它名称: | 2008BVLFT |

ICS2008B

8

ICS2008B

Video Control Register IR32

GENLOCK ENABLE — When set to one, this bit enables

the genlock circuits to sync to the selected video input signal.

When reset to 0, the video sync will “freewheel,” generating

video timing from the internal oscillator. The freewheel mode

would be selected when striping LTC to allow synchroni-

zation with a MIDI sequencer or other strictly timed audio

source.

VTRES — When set to one, this bit clears the video timing

counters to dot zero of line 1 of field 1. This is useful when the

video is free running, not genlocked and LTC sync needs to be

synchronized to an event such as the CLICK input.

VSYNCSEL — When set to one, this bit selects the video

input source from Video2 (Y2) to be the SYNC source for the

internal video timing. Otherwise, when reset to zero, Video1

(Y1) is selected.

VITCSEL — When set to one, this bit selects the video input

source from Video2 (Y2) to be the VITC time code source for

the VITC receiver. Otherwise, when reset to zero, Video1

(Y1) is selected.

VOUTSEL — When set to one, this bit selects the video

input source from Video2 (Y2, C2) to be output on the video

outputs (YOUT, COUT). When reset to zero, Video1 (Y1,

C1) are selected.

VID1_S — When set to one, this bit causes the Video1 source

to be treated as S-Video. Otherwise, when cleared to zero, the

Video1 source is treated as composite video.

VID2_S — When set to one, this bit causes the Video2 source

to be treated as S-Video. Otherwise, when cleared to zero, the

Video2 source is treated as composite video.

VITC Read Line Select Registers IR30-IR31

As with the VITC Write Line Register, these registers allow

control of the individual redundant VITC read lines. The

processor can also reprogram these dynamically to allow for

scanning of VITC code when the source lines are unknown.

Read Line – Selects the line from which VITC code is to be

read within each field. It works identically to the Write Line

in that the video line selected is the number in this register

plus 10.

Auto line scanning is enabled by writing a 1Fh to the Read

Line field. This causes the VITC reader to search for time

code. If VITC Read Line 1 is set to search, it starts with line

10 and quits when it finds a valid time code or when it reaches

line 41. Searching with VITC Read Line 2 starts after VITC

Read Line 1. In the case of searching for both VITC Read

Lines 1 and 2, VITC Read Line 2 starts searching after the

first valid time code has been found. However, if VITC Read

Line 1 is set to a specific line, VITC Read Line 2 starts after

that specified line regardless of whether valid time code was

received. In any case, the search terminates after line 41.

CRCERR — This bit is reset to zero when a valid VITC code

has been received. It is valid from the end of the selected

video line until the end of the selected line in the next field.

NOCODE — This bit is set when a framing error occurs in

the VITC code, i.e. not all the bits of the code were received

by the time the end of the video line occurred. Both CRCERR

and NOCODE must be zero to qualify a VITC code.

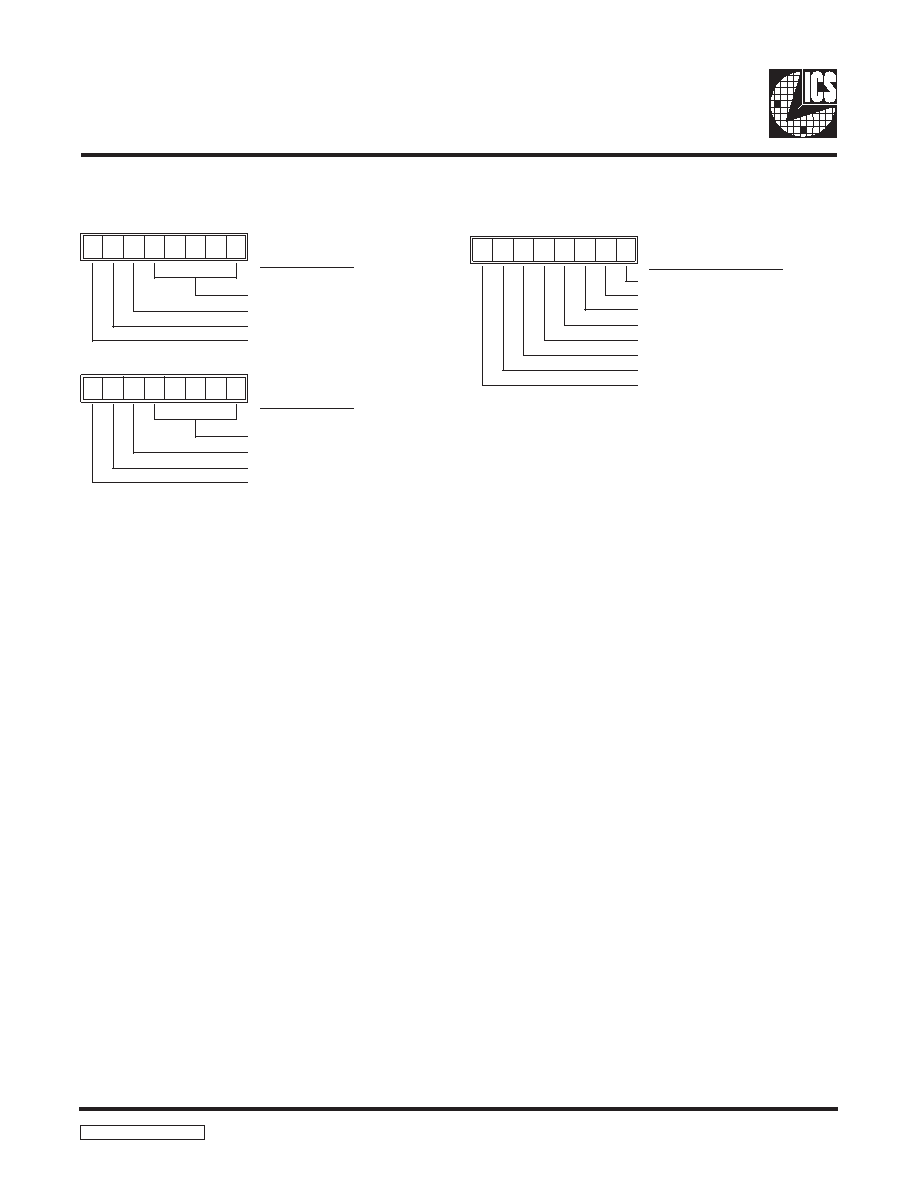

Video Control Register

GENLOCK ENABLE (1-lock, 0-freewheel)

VTRES - Video Timing Reset (1-reset)

VSYNCEL - Video SYNC Source Select

VITCSEL - VITC Source Select

VOUTSEL - Video Output Select

VID1_S - Video1 S-Video Select

VID2_S - Video2 S-Video Select

PAL/NTSC (1-PAL, 0-NTSC)

7

6

5

4

3

2

1

0

IR32

VITC Read Line 1

Read Line 10-40 (N+10)

CRCERR (1-error, 0-OK) (r/o)

NOCODE (1-no code, 0-code) (r/o)

VITC Read Enable (1-enable)

IR30

7

6

5

4

3

2

1

0

VITC Read Line 2

Read Line 10-40 (N+10)

CRCERR (1-error, 0-OK) (r/o)

NOCODE (1-no code, 0-code) (r/o)

VITC Read Enable (1-enable)

IR31

7

6

5

4

3

2

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| VE-27H-IW-F4 | CONVERTER MOD DC/DC 52V 100W |

| VE-27H-IW-F3 | CONVERTER MOD DC/DC 52V 100W |

| T 3475 005 | CONN MALE 7POS CABLE MNT R/A |

| VE-J4M-MY-F3 | CONVERTER MOD DC/DC 10V 50W |

| VE-J4K-MY-F2 | CONVERTER MOD DC/DC 40V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS2008BVT | 功能描述:IC TIME CODE RCVR/GEN 44-PLCC RoHS:否 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| ICS2008BY-10 | 功能描述:IC TIME CODE RCVR/GEN 44-TQFP RoHS:否 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| ICS2008BY-10LF | 功能描述:IC TIME CODE RCVR/GEN 44-TQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 标准包装:250 系列:- 类型:电平移位器 应用:LCD 电视机/监控器 安装类型:表面贴装 封装/外壳:28-WFQFN 裸露焊盘 供应商设备封装:28-WQFN(4x4)裸露焊盘 包装:带卷 (TR) 其它名称:296-32523-2TPS65198RUYT-ND |

| ICS2008BY-10LFT | 功能描述:IC TIME CODE RCVR/GEN 44-TQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

| ICS2008BY-10T | 功能描述:IC TIME CODE RCVR/GEN 44-TQFP RoHS:否 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 产品变化通告:Product Discontinuation 07/Mar/2011 标准包装:3,000 系列:OMNITUNE™ 类型:调谐器 应用:移动电话,手机,视频显示器 安装类型:表面贴装 封装/外壳:65-WFBGA 供应商设备封装:PG-WFSGA-65 包装:带卷 (TR) 其它名称:SP000365064 |

发布紧急采购,3分钟左右您将得到回复。