- 您现在的位置:买卖IC网 > PDF目录67685 > ICS252MI-XX (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, OTHER CLOCK GENERATOR, PDSO8 PDF资料下载

参数资料

| 型号: | ICS252MI-XX |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| 封装: | 150 INCH, SOIC-8 |

| 文件页数: | 4/11页 |

| 文件大小: | 210K |

| 代理商: | ICS252MI-XX |

ICS252

FIELD PROGRAMMABLE DUAL OUTPUT SS VERSACLOCK SYNTHESIZER

EPROM CLOCK SYNTHESIZER

IDT / ICS FIELD PROGRAMMABLE DUAL OUTPUT SS VERSACLOCK SYNTHESIZER 2

ICS252

REV E 082007

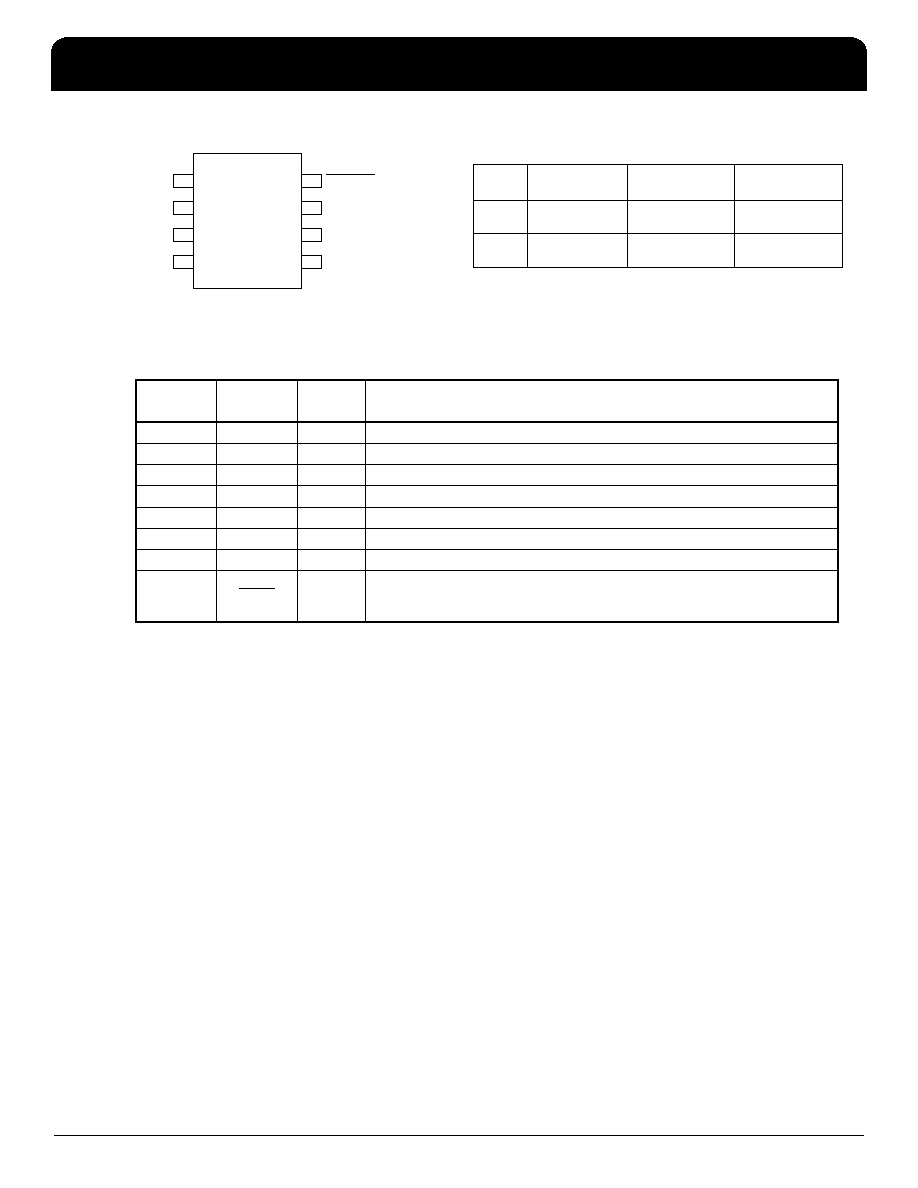

Pin Assignment

8-pin (150 mil) SOIC

Output Clock Selection Table

Pin Descriptions

External Components

The ICS252 requires a minimum number of external

components for proper operation.

Series Termination Resistor

Clock output traces over one inch should use series

termination. To series terminate a 50

trace (a commonly

used trace impedance), place a 33

resistor in series with

the clock line, as close to the clock output pin as possible.

The nominal impedance of the clock output is 20

.

Decoupling Capacitor

As with any high-performance mixed-signal IC, the ICS252

must be isolated from system power supply noise to perform

optimally.

A decoupling capacitor of 0.01F must be connected

between VDD and the PCB ground plane.

Crystal Load Capacitors

The device crystal connections should include pads for

small capacitors from X1 to ground and from X2 to ground.

These capacitors are used to adjust the stray capacitance

of the board to match the nominally required crystal load

capacitance. Because load capacitance can only be

increased in this trimming process, it is important to keep

stray capacitance to a minimum by using very short PCB

traces (and no vias) been the crystal and device. Crystal

capacitors must be connected from each of the pins X1 and

X2 to ground.

The value (in pF) of these crystal caps should equal (CL -6

pF)*2. In this equation, CL= crystal load capacitance in pF.

Example: For a crystal with a 16 pF load capacitance, each

crystal capacitor would be 20 pF [(16-6) x 2 = 20].

PCB Layout Recommendations

For optimum device performance and lowest output phase

X 1 /IC L K

VD D

G N D

SEL

CL K 2

CL K 1

X2

1

2

3

4

8

7

6

5

PD T S

SEL

CLK1 (MHz)

CLK2 (MHz)

Spread

Percentage

0

User

Configurable

User

Configurable

User

Configurable

1User

Configurable

User

Configurable

User

Configurable

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

SEL

Input

Select pin for frequency selection on CLK1 and CLK2. Internal pull-up resistor.

2

VDD

Power

Connect to +3.3 V.

3

X1/ICLK

XI

Connect this pin to a crystal or external clock input.

4

X2

XO

Connect this pin to a crystal, or float for clock input.

5

CLK1

Output

Clock1 output. Weak internal pull-down, low when power down.

6

CLK2

Output

Clock2 output. Weak internal pull-down, low when power down.

7

GND

Power

Connect this to ground.

8PDTS

Input

Powers down entire chip. Tri-states CLK outputs when low. No internal pull-up

resistor. The pin must be tied either directly or through the external resistor to

VDD ro GND. External resistor value must be less than 15kOhm.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS252PMI | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS252PMT | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS271GI-XXLF | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS271GI-XXT | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| ICS271PGLF | 200 MHz, OTHER CLOCK GENERATOR, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS252MI-XXLF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FIELD PROGRAMMABLE DUAL OUTPUT SS VERSACLOCK SYNTHESIZER |

| ICS252MI-XXLFT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FIELD PROGRAMMABLE DUAL OUTPUT SS VERSACLOCK SYNTHESIZER |

| ICS252MI-XXT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FIELD PROGRAMMABLE DUAL OUTPUT SS VERSACLOCK SYNTHESIZER |

| ICS252MP | 制造商:ICS 制造商全称:ICS 功能描述:Field Programmable Dual Output SS VersaClock Synthesizer |

| ICS252MPLF | 制造商:ICS 制造商全称:ICS 功能描述:Field Programmable Dual Output SS VersaClock Synthesizer |

发布紧急采购,3分钟左右您将得到回复。