- 您现在的位置:买卖IC网 > PDF目录1996 > ICS270PGILF (IDT, Integrated Device Technology Inc)VCXO CLK TRPL PLL PROGR 20-TSSOP PDF资料下载

参数资料

| 型号: | ICS270PGILF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 4/11页 |

| 文件大小: | 0K |

| 描述: | VCXO CLK TRPL PLL PROGR 20-TSSOP |

| 标准包装: | 74 |

| 系列: | VersaClock™ |

| 类型: | 时钟/频率合成器,扇出缓冲器(分配) |

| PLL: | 带旁路 |

| 输入: | 晶体 |

| 输出: | CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:8 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 200MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

| 其它名称: | 270PGILF |

ICS270

TRIPLE PLL FIELD PROGRAMMABLE VCXO CLOCK

EPROM VCXO AND SYNTHESIZER

IDT / ICS TRIPLE PLL FIELD PROGRAMMABLE VCXO CLOCK

2

ICS270

REV F 051310

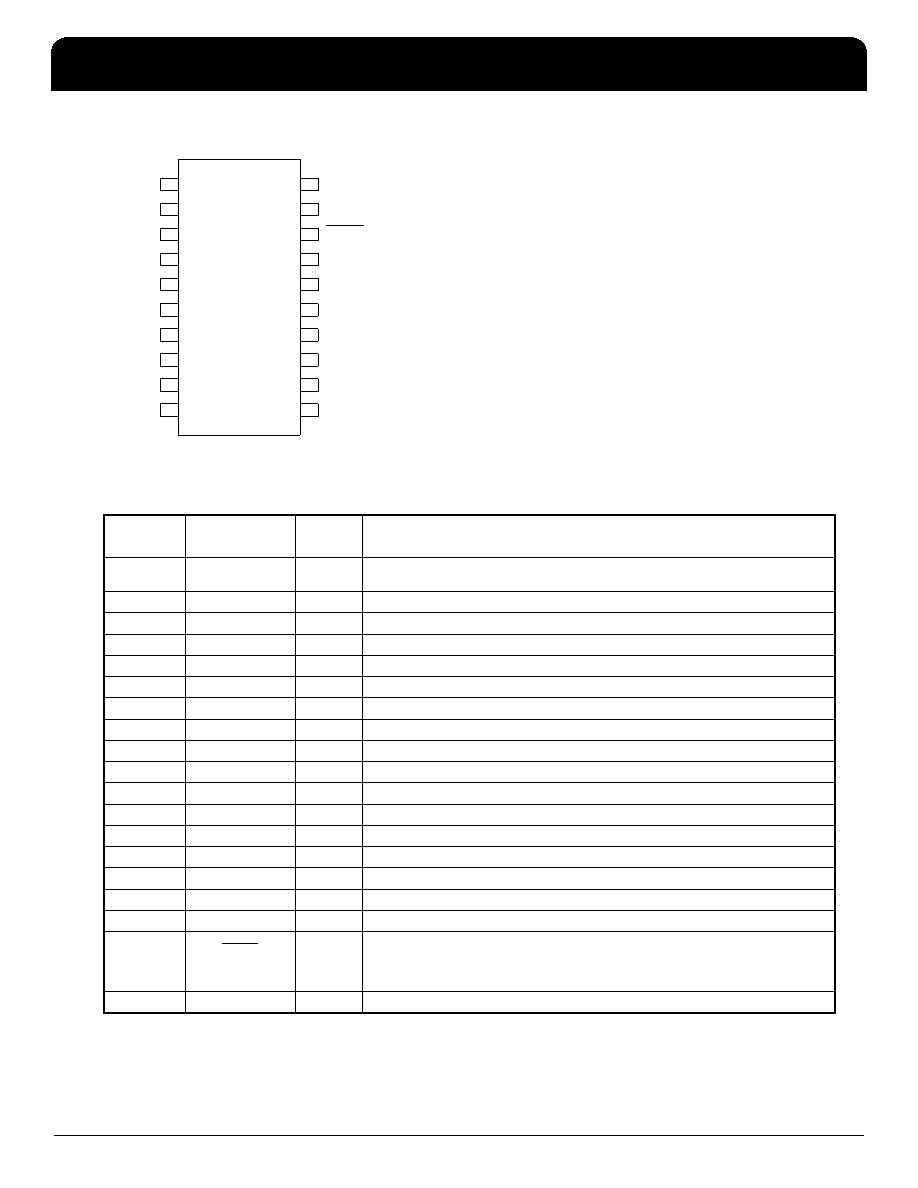

Pin Assignment

Pin Descriptions

13

4

12

5

11

VDD

8

9

10

GND

CLK3

CLK7

CLK1

CLK4

CLK8

17

16

CLK5

3

S1

VIN

S2

18

PDTS

1

X1

S0

VDD

20

X2

19

14

2

7

GND

CLK2

VDD

CLK6

15

6

20 pin (173 mil) TSSOP

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

VIN

Input

Voltage input to VCXO. Zero to 3.3V signal which controls the VCXO

frequency

2

S0

Input

Select pin 0. Internal pull-up resistor.

3

S1

Input

Select pin 1. Internal pull-up resistor.

4VDD

Power

Connect to +3.3 V.

5

CLK1

Output

Output clock 1. Weak internal pull-down when tri-state.

6

CLK2

Output

Output clock 2. Weak internal pull-down when tri-state.

7

CLK3

Output

Output clock 3. Weak internal pull-down when tri-state.

8

CLK4

Output

Output clock 4. Weak internal pull-down when tri-state.

9

GND

Power

Connect to ground.

10

X1

XI

Crystal input. Connect this pin to a crystal.

11

X2

XO

Crystal Output. Connect this pin to a crystal.

12

VDD

Power

Connect to +3.3 V.

13

CLK5

Output

Output clock 5. Weak internal pull-down when tri-state.

14

CLK6

Output

Output clock 6. Weak internal pull-down when tri-state.

15

CLK7

Output

Output clock 7. Weak internal pull-down when tri-state.

16

CLK8

Output

Output clock 8. Weak internal pull-down when tri-state.

17

GND

Power

Connect to ground.

18

PDTS

Input

Power-down tri-state. Powers down entire chip and tri-states clock outputs

when low. Internal pull-up resisitor.

19

VDD

Power

Connect to +3.3 V.

20

S2

Input

Select pin 2. Internal pull-up resisitor.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS281PGILF | IC CLK SYNTH TRPL PLL 16-TSSOP |

| ICS411MLF | IC PC PERIPHERAL CLOCK 8-SOIC |

| ICS477R-05T | IC QUAD PLL VCXO FOR HDTV 28QSOP |

| ICS487G-25T | IC QUAD PLL FOR DTV 16-TSSOP |

| ICS501AMILF | IC PLL CLK MULTIPLIER 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS270PGILFT | 功能描述:VCXO CLK TRPL PLL PROGR 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS270PGIT | 功能描述:VCXO CLK TRPL PLL PROGR 20-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS270PGLF | 功能描述:VCXO CLK TRPL PLL PROGR 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS270PGLFT | 功能描述:VCXO CLK TRPL PLL PROGR 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS270PGT | 功能描述:VCXO CLK TRPL PLL PROGR 20-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。