- 您现在的位置:买卖IC网 > PDF目录65529 > ICS525RI12LFT 50 MHz, OTHER CLOCK GENERATOR, PDSO28 PDF资料下载

参数资料

| 型号: | ICS525RI12LFT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 50 MHz, OTHER CLOCK GENERATOR, PDSO28 |

| 封装: | 0.150 INCH, LEAD FREE, MO-153, SSOP-28 |

| 文件页数: | 8/9页 |

| 文件大小: | 178K |

| 代理商: | ICS525RI12LFT |

User Configurable Clock

MDS 525-01/02/11/12 R

8

Revision 042506

Integrated Circuit Systems, Inc.

● 525 Race Street, San Jose, CA 95126 ● tel (408) 297-1201 ● www.icst.com

ICS525-01/02/11/12

NOTE 1: Phase relationship between input and output can change at power-up. For a fixed phase

relationship, see the ICS527.

NOTE 2: For 16 MHz, 100 MHz output. Use the -02 for lowest jitter.

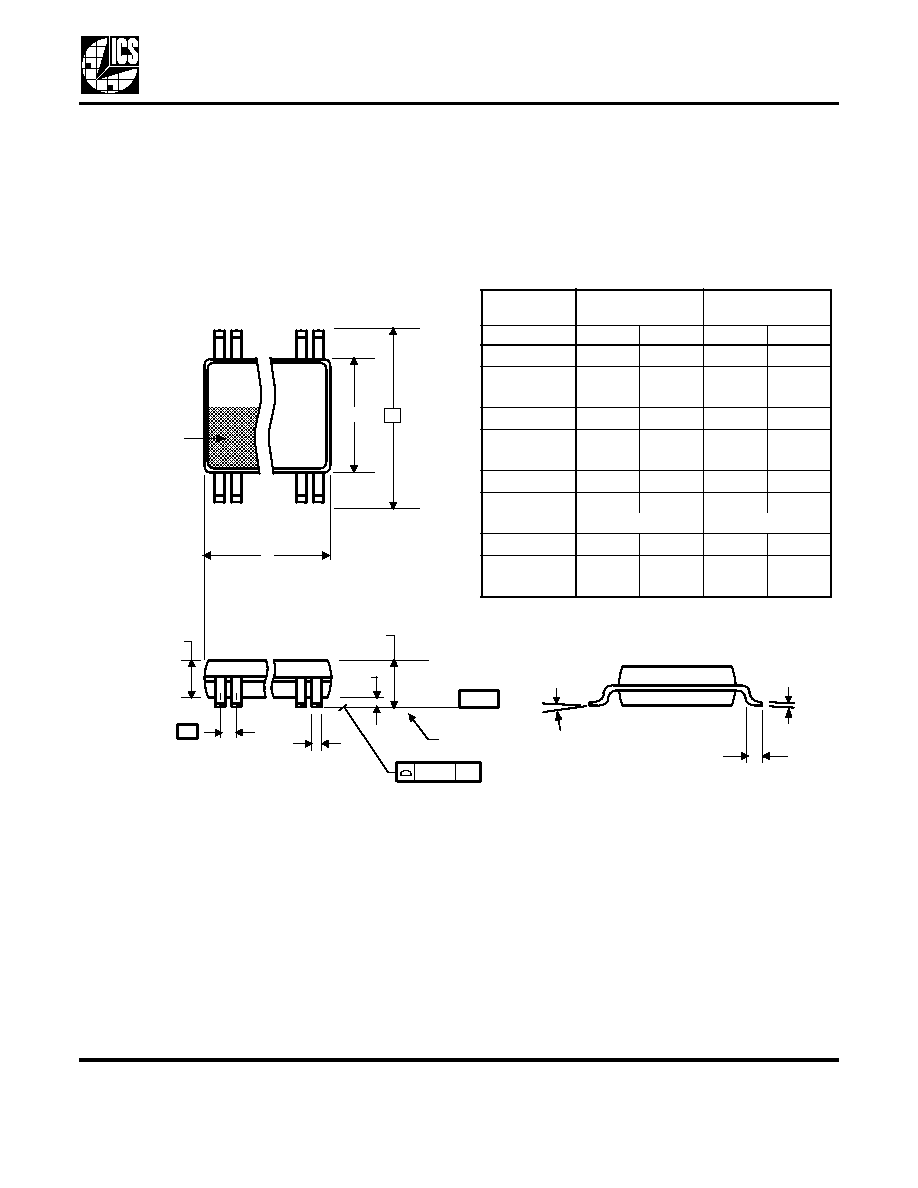

Package Outline and Package Dimensions (28-pin SSOP, 150 mil Body)

Package dimensions are kept current with JEDEC Publication No. 95, MO-153

INDEX

AREA

1 2

28

D

E1

E

SEATING

PLANE

A

1

A

2

e

- C -

b

aaa C

c

L

*For reference only. Controlling dimensions in mm.

Millimeters

Inches*

Symbol

Min

Max

Min

Max

A

1.351.75.053

.069

A1

0.10

0.25

.0040

.010

A2

--

1.50

--

.059

b

0.200.30.008

.012

C

0.180.25.007

.010

D

9.80

10.00

.386

.394

E

5.806.20.228

.244

E1

3.80

4.00

.150

.157

e

0.635 Basic

0.025 Basic

L

0.401.27.016

.050

α

0

°

8

°

0

°

8

°

aaa

--

0.10

--

0.004

相关PDF资料 |

PDF描述 |

|---|---|

| ICS525-01RLF | 160 MHz, OTHER CLOCK GENERATOR, PDSO28 |

| ICS525R-02LF | 250 MHz, OTHER CLOCK GENERATOR, PDSO28 |

| ICS527R-01IT | 527 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ICS527R-01LFT | 527 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ICS527R-01LFT | 527 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS525RI-12T | 制造商:ICS 制造商全称:ICS 功能描述:User Configurable Clock |

| ICS527-01 | 制造商:ICS 制造商全称:ICS 功能描述:Clock Slicer⑩ User Configurable Zero Delay Buffer |

| ICS527-02 | 制造商:ICS 制造商全称:ICS 功能描述:Clock Slicer User Configurable PECL Input Zero Delay Buffer |

| ICS527-03 | 制造商:ICS 制造商全称:ICS 功能描述:Clock Slicer User Configurable PECL Output Zero Delay Buffer |

| ICS527-04 | 制造商:ICS 制造商全称:ICS 功能描述:Clock Slicer User Configurable PECL input Zero Delay Buffer |

发布紧急采购,3分钟左右您将得到回复。