- 您现在的位置:买卖IC网 > PDF目录65530 > ICS571MLF (INTEGRATED DEVICE TECHNOLOGY INC) 571 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 PDF资料下载

参数资料

| 型号: | ICS571MLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 571 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 封装: | 0.150 INCH, ROHS COMPLIANT, SOIC-8 |

| 文件页数: | 5/7页 |

| 文件大小: | 184K |

| 代理商: | ICS571MLF |

ICS571

LOW PHASE NOISE ZERO DELAY BUFFER

ZDB AND MULTIPLIER/DIVIDER

IDT / ICS LOW PHASE NOISE ZERO DELAY BUFFER

5

ICS571

REV F 062306

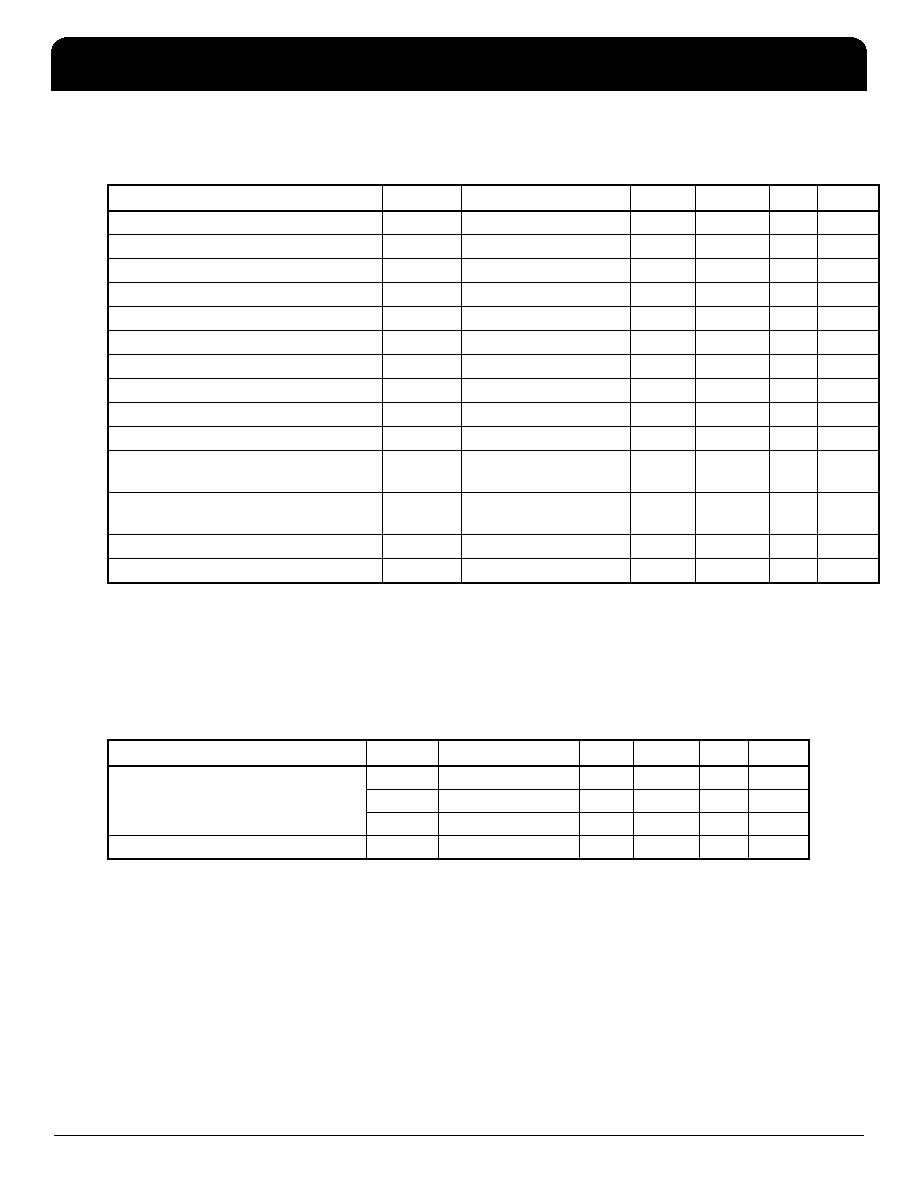

AC Electrical Characteristics

Unless stated otherwise, VDD = 5.0 V or 3.3 V, Ambient Temperature 0 to +70

° C

Notes:

1. Sresses beyond these can permanently damage the device.

2. Assumes clocks with the same rise time, measured from rising edges at VDD/2. Measured with 33

termination

resistors and 15 pF loads. Applies to both 3.3 V and 5 V operation.

3. CLK/2 has lower jitter (both absolute and one sigma, in ps) than CLK.

Thermal Characteristics

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Input Frequency, clock input

fIN

FB from CLK

20

160

MHz

Input Frequency, clock input

fIN

FB from CLK/2

10

80

MHz

Skew CLK/2 with respect to CLK

Note 2

150

500

850

ps

Input clock to output connected to FBIN

Note 2

-500

500

ps

Output Clock Rise Time, 5 V

0.8 to 2.0 V, 15 pF load

0.3

ns

Output Clock Fall Time, 5 V

2.0 to 0.8 V, 15 pF load

0.4

ns

Output Clock Rise Time, 3.3 V

0.8 to 2.0 V, 15 pF load

0.45

ns

Output Clock Fall Time, 3.3 V

2.0 to 0.8 V, 15 pF load

0.55

ns

Input Clock Duty Cycle, 3.3 V

fin = 150 MHz

20

80

%

Output Clock Duty Cycle, 3.3 V

At VDD/2

45

49 to 51

55

%

Absolute Clock Period Jitter, CLK,

Note 3

Deviation from Mean

±80

ps

One-Sigma Clock Period Jitter, CLK,

Note 3

50

ps

Phase Noise, Relative to carrier

1 kHz offset

-105

dBc/Hz

Phase Noise, Relative to carrier

100 kHz offset

-115

dBc/Hz

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Thermal Resistance Junction to

Ambient

θ

JA

Still air

°C/W

θ

JA

1 m/s air flow

°C/W

θ

JA

3 m/s air flow

°C/W

Thermal Resistance Junction to Case

θ

JC

°C/W

相关PDF资料 |

PDF描述 |

|---|---|

| ICS571M | 571 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS574MILF | 574 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS574MLFT | 574 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS574M | 574 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS574MLFT | 574 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS571MLFT | 功能描述:IC BUFFER ZD LOW PH/NOISE 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:ClockBlocks™ 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ICS571MT | 功能描述:IC MULTIPLIER/ZDB 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:ClockBlocks™ 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS574 | 制造商:ICS 制造商全称:ICS 功能描述:Zero Delay, Low Skew Buffer |

| ICS574M | 功能描述:IC CLOCK ZDB 1:4 160MHZ 8SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS574MI | 功能描述:IC CLOCK ZDB 1:4 160MHZ 8SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。