- 您现在的位置:买卖IC网 > PDF目录65531 > ICS663MILF 663 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 PDF资料下载

参数资料

| 型号: | ICS663MILF |

| 元件分类: | 时钟及定时 |

| 英文描述: | 663 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 封装: | 0.150 INCH, ROHS COMPLIANT, SOIC-8 |

| 文件页数: | 1/7页 |

| 文件大小: | 146K |

| 代理商: | ICS663MILF |

ICS663

MDS 663 E

1

Revision 012006

Integrat ed Circuit Systems ● 525 Race Stre et, San Jo se, CA 9 5126 ● te l (40 8 ) 2 97-12 01 ● www.ics t.co m

PLL BUILDING BLOCK

Description

The ICS663 is a low cost Phase-Locked Loop (PLL)

designed for clock synthesis and synchronization.

Included on the chip are the phase detector, charge

pump, Voltage Controlled Oscillator (VCO) and an

output buffer. Through the use of external reference

and VCO dividers (implemented with the ICS674-01,

for example), the user can easily configure the device

to lock to a wide variety of input frequencies.

The phase detector and VCO functions of the device

can also be used independently. This enables the

configuration of other PLL circuits. For example, the

ICS663 phase detector can be used to control a VCXO

circuit such as the MK3754.

For applications requiring Power Down or Output

Enable features, please refer to the ICS673-01.

Features

Packaged in 8-pin SOIC (Pb free)

Output clock range 1 MHz to 100 MHz (3.3 V), 1 MHz

to 120 MHz (5 V)

External PLL loop filter enables configuration for a

wide range of input frequencies

Ability to accept an input clock in the kHz range

(video Hsync, for example)

25 mA output drive capability at TTL levels

Lower power CMOS process

+3.3 V ±5% or +5 V ±10% operating voltage

Used along with the ICS674-01, forms a complete

PLL circuit

Phase detector and VCO blocks can be used

independently for other PLL configurations

Industrial temperature version available

For better jitter performance, use the MK1575

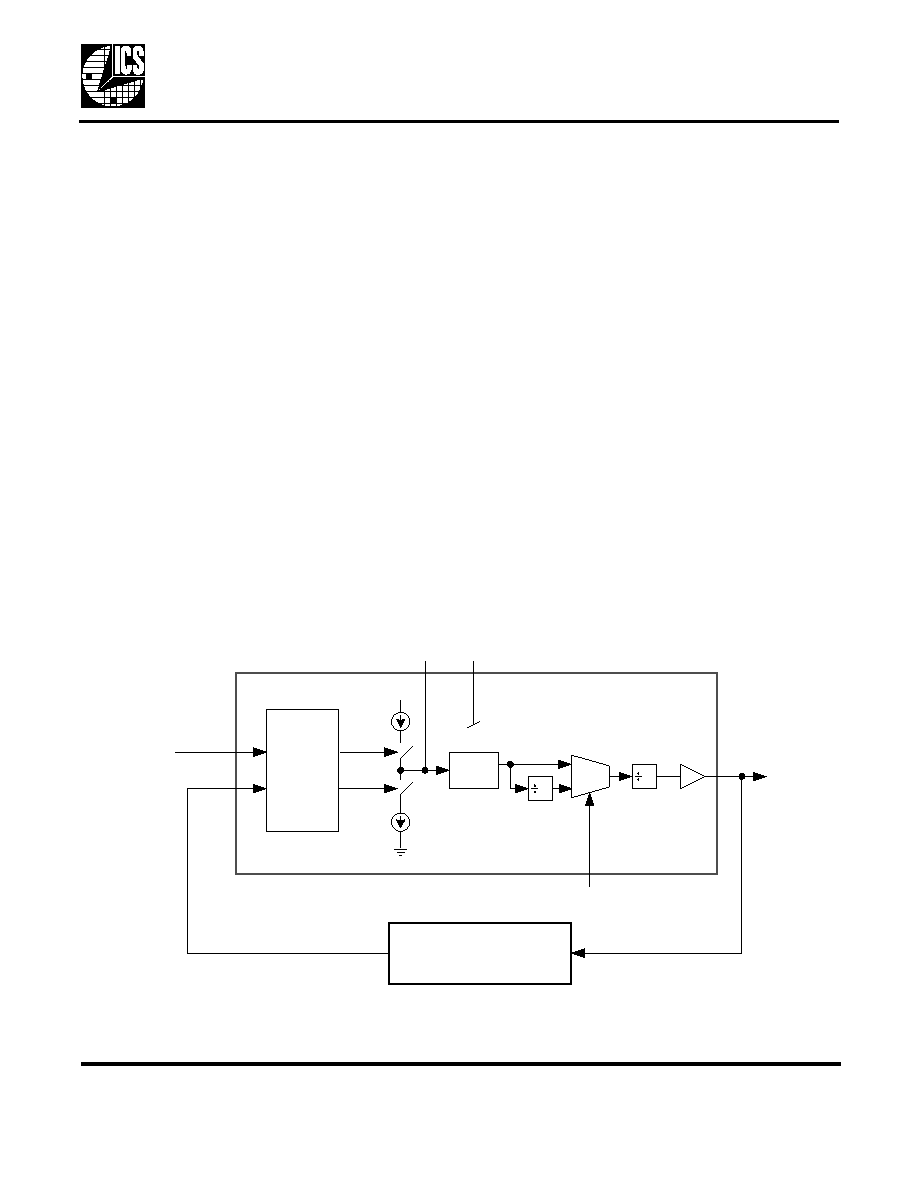

Block Diagram

REF IN

P hase/

Frequency

De te cto r

VCO

4

2

SEL

LFR

LF

UP

FBIN

DOW N

I

cp

I

cp

CL K

VDD

MU X

1

0

E xternal F eedback D ivider

(such as the IC S 674-01)

C lock Input

相关PDF资料 |

PDF描述 |

|---|---|

| ICS663MT | PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS663M | PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS664G-03LFT | 148.5 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS664G-03T | 148.5 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS664G-03 | 148.5 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS663MILFT | 功能描述:IC PLL BUILDING BLOCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ICS663MIT | 功能描述:IC PLL BUILDING BLOCK 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS663MLF | 功能描述:IC PLL BUILDING BLOCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ICS663MLFT | 功能描述:IC PLL BUILDING BLOCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| ICS663MT | 功能描述:IC PLL BUILDING BLOCK 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。