- 您现在的位置:买卖IC网 > PDF目录67110 > ICS672MI-02LFT (INTEGRATED DEVICE TECHNOLOGY INC) 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | ICS672MI-02LFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, SOIC-16 |

| 文件页数: | 1/8页 |

| 文件大小: | 190K |

| 代理商: | ICS672MI-02LFT |

DATASHEET

QUADRACLOCK QUADRATURE DELAY BUFFER

ICS672-01/02

IDT / ICS QUADRACLOCK QUADRATURE DELAY BUFFER

1

ICS672-01/02

REV G 092506

Description

The ICS672-01/02 are zero delay buffers that generate four

output clocks whose phases are spaced at 90° intervals.

Based on IDT’s proprietary low jitter Phase-Locked Loop

(PLL) techniques, each device provides five low-skew

outputs, with clock rates up to 84 MHz for the ICS672-01

and up to 135 MHz for the ICS672-02. By providing outputs

delayed one quarter clock cycle, the device is useful for

systems requiring early or late clocks. The ICS672-01/02

include multiplier selections of x0.5, x1, x2, x3, x4, x5, or x6.

They also offer a mode to power-down all internal circuitry

and tri-state the outputs. In normal operation, output clock

FBCLK is tied to the FBIN pin.

IDT manufactures the largest variety of clock generators

and buffers, and is the largest clock supplier in the world.

Features

Packaged in 16-pin SOIC

Available in Pb (lead) free package

Input clock range from 5 MHz to 150 MHz (depends on

multiplier)

Clock outputs from up to 84 MHz (ICS672-01) and up to

135 MHz (ICS672-02)

Zero input-output delay

Integrated x0.5, x1, x2, x3, x4, x5, or x6 selections

Four accurate (<250 ps) outputs with 0°, 90°, 180°, and

270° phase shift from ICLK, and one FBCLK (0°)

Separate supply for output clocks from 2.5 V to 5 V

Full CMOS outputs (TTL compatible)

Tri-state mode for board-level testing

Includes Power-down for power savings

Advanced, low power, sub-micron CMOS process

3.3 V to 5 V operating voltage

Industrial temperature version available

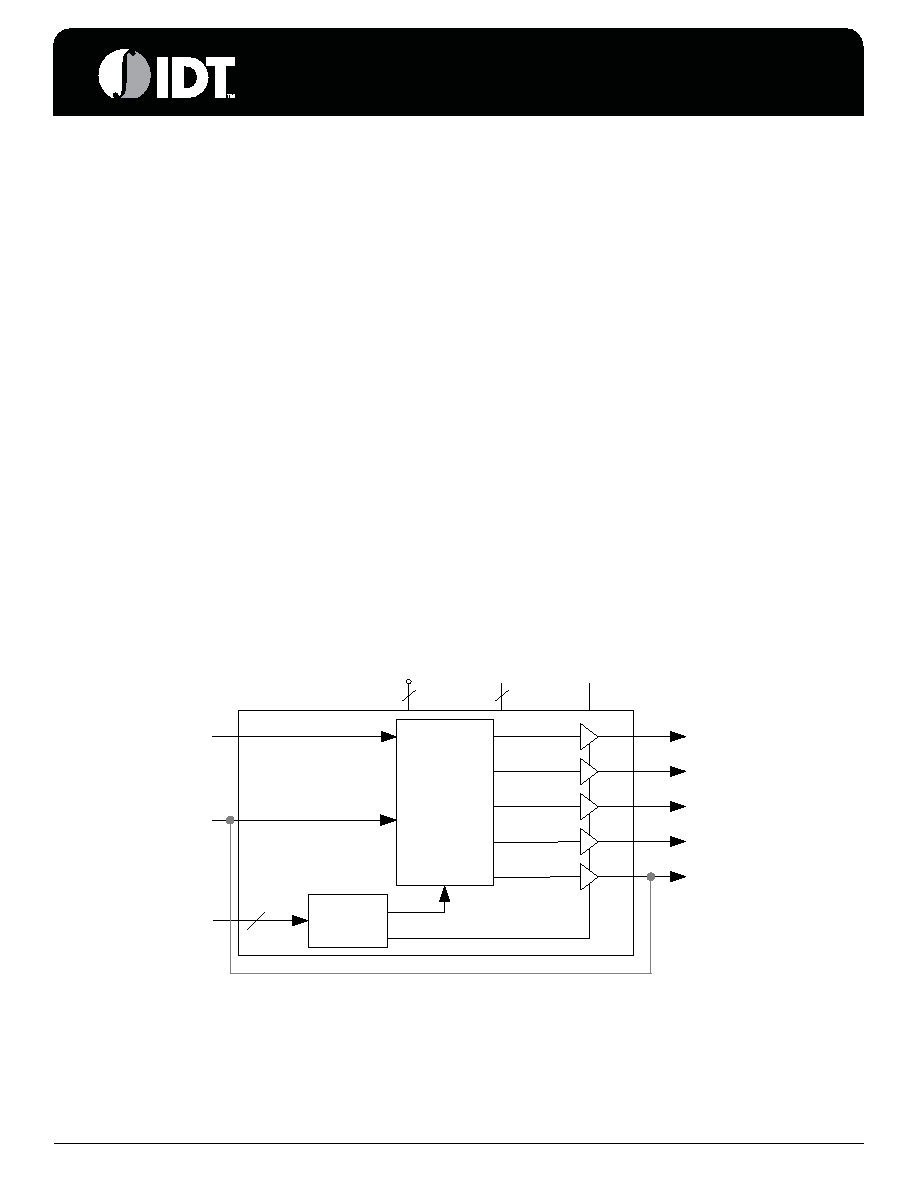

Block Diagram

Control

Logic

CLK0

VDDIO

PLL

Multiplier

and

Quadrature

Generation

FBIN

S2:S0

IN

CLKFB

3

Power Down plus Tri-state

VDD

2

External

Feedback

GND

3

CLK90

CLK180

CLK270

相关PDF资料 |

PDF描述 |

|---|---|

| ICS672M-01 | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS673-01MT | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS673-01M | PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS674R-01LF | SPECIALTY LOGIC CIRCUIT, PDSO28 |

| ICS674R-01LFT | SPECIALTY LOGIC CIRCUIT, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS673-01 | 制造商:ICS 制造商全称:ICS 功能描述:PLL Building Block |

| ICS673M-01 | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS673M-01I | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS673M-01ILF | 功能描述:IC PLL BUILDING BLOCK 16SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ICS673M-01ILFT | 功能描述:IC PLL BUILDING BLOCK 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。