- 您现在的位置:买卖IC网 > PDF目录67690 > ICS84321AYLFT 260 MHz, OTHER CLOCK GENERATOR, PQFP32 PDF资料下载

参数资料

| 型号: | ICS84321AYLFT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 260 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| 封装: | 7 X 7 MM, 1.40 MM HEIGHT, LEAD FREE, MS-026, LQFP-32 |

| 文件页数: | 4/18页 |

| 文件大小: | 204K |

| 代理商: | ICS84321AYLFT |

84321AY

www.icst.com/products/hiperclocks.html

REV. B JUNE 9, 2005

12

Integrated

Circuit

Systems, Inc.

ICS84321

260MHZ, CRYSTAL-TO-3.3V DIFFERENTIAL

LVPECL FREQUENCY SYNTHESIZER

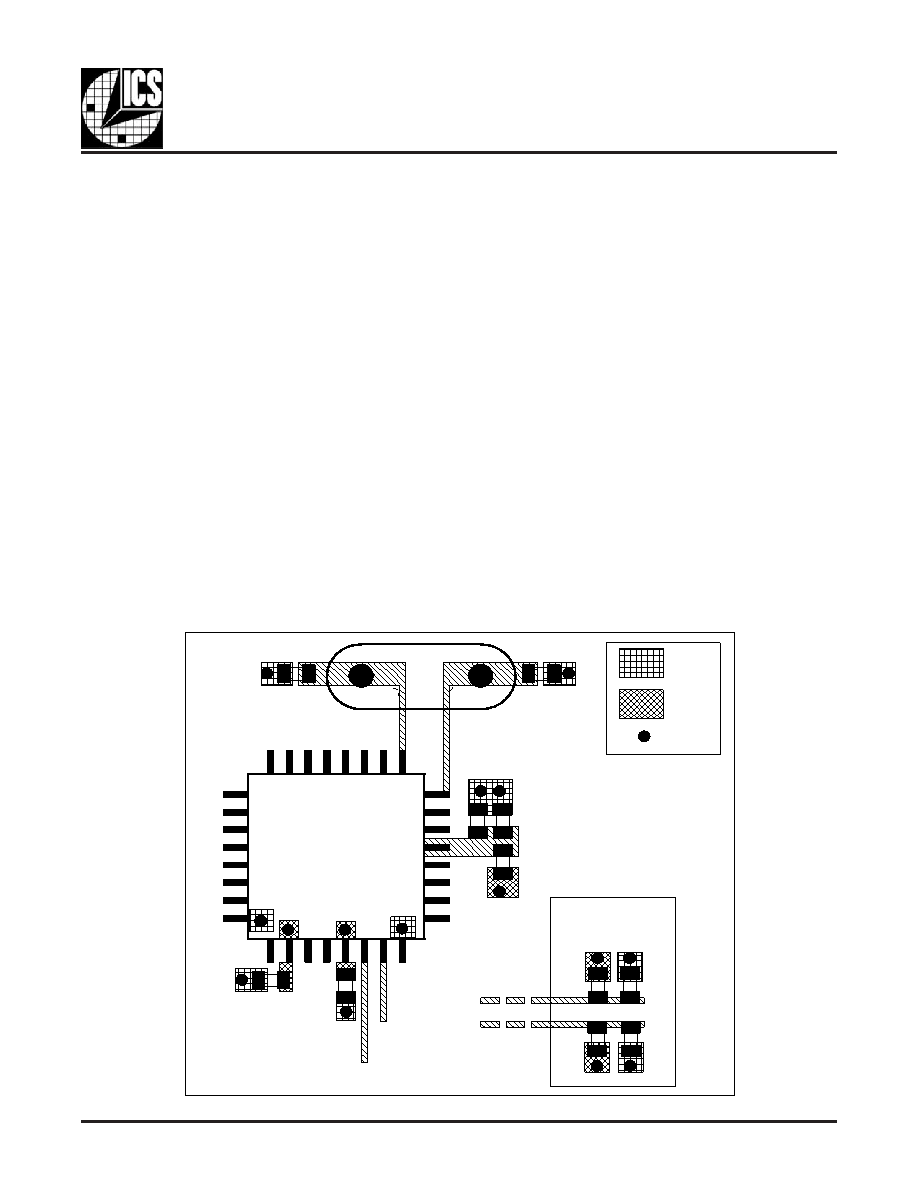

FIGURE 5B. PCB BOARD LAYOUT FOR ICS84321

The following component footprints are used in this layout

example:

All the resistors and capacitors are size 0603.

POWER AND GROUNDING

Place the decoupling capacitors C14 and C15, as close as pos-

sible to the power pins. If space allows, placement of the

decoupling capacitor on the component side is preferred. This

can reduce unwanted inductance between the decoupling ca-

pacitor and the power pin caused by the via.

Maximize the power and ground pad sizes and number of vias

capacitors. This can reduce the inductance between the power

and ground planes and the component power and ground pins.

The RC filter consisting of R7, C11, and C16 should be placed

as close to the V

CCA pin as possible.

CLOCK TRACES AND TERMINATION

Poor signal integrity can degrade the system performance or

cause system failure. In synchronous high-speed digital systems,

the clock signal is less tolerant to poor signal integrity than other

signals. Any ringing on the rising or falling edge or excessive ring

back can cause system failure. The shape of the trace and the

trace delay might be restricted by the available space on the board

and the component location. While routing the traces, the clock

signal traces should be routed first and should be locked prior to

routing other signal traces.

The differential 50

Ω output traces should have the

same length.

Avoid sharp angles on the clock trace. Sharp angle

turns cause the characteristic impedance to change on

the transmission lines.

Keep the clock traces on the same layer. Whenever pos-

sible, avoid placing vias on the clock traces. Placement

of vias on the traces can affect the trace characteristic

impedance and hence degrade signal integrity.

To prevent cross talk, avoid routing other signal traces in

parallel with the clock traces. If running parallel traces is

unavoidable, allow a separation of at least three trace

widths between the differential clock trace and the other

signal trace.

Make sure no other signal traces are routed between the

clock trace pair.

The matching termination resistors should be located as

close to the receiver input pins as possible.

CRYSTAL

The crystal X1 should be located as close as possible to the pins

25 (XTAL_IN) and 24 (XTAL_OUT).The trace length between the

X1 and U1 should be kept to a minimum to avoid unwanted

parasitic inductance and capacitance. Other signal traces should

not be routed near the crystal traces.

T

L1N

R2

TL1, TL21N are 50 Ohm

traces and equal length

U1

R1

TL1

C1

TL

1

GND

R7

C16

TL1N

VCC

R3

Close to the input

pins of the

receiver

C11

X1

C2

C14

VIA

R4

C15

VCCA

PIN 1

相关PDF资料 |

PDF描述 |

|---|---|

| ICS843246AMIT | 333.33 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS843246AMLFT | 333.33 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS843246AGT | 333.33 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS843246AMLF | 333.33 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS84324AMLFT | 125 MHz, OTHER CLOCK GENERATOR, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS84321AYT | 制造商:ICS 制造商全称:ICS 功能描述:260MHZ, CRYSTAL-TO-3.3V DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER |

| ICS84321I | 制造商:ICS 制造商全称:ICS 功能描述:260MHZ, CRYSTAL-TO-3.3V DIFFERENTIAL LVPECL FREQUENCY SYNTHESIZER |

| ICS84324 | 制造商:ICS 制造商全称:ICS 功能描述:CRYSTAL-TO-3.3V LVPECL FREQUENCY SYNTHESIZER WITH FANOUT BUFFER |

| ICS843241I-04 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FEMTOCLOCKSa?¢ CRYSTAL-TO-3.3V, 2.5V LVPECL CLOCK GENERATOR |

| ICS843242 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:FEMTOCLOCKS⑩ CRYSTAL-TO-3.3V LVPECL FREQUENCY SYNTHESIZER |

发布紧急采购,3分钟左右您将得到回复。