- 您现在的位置:买卖IC网 > PDF目录67691 > ICS84326AMLF 150 MHz, OTHER CLOCK GENERATOR, PDSO24 PDF资料下载

参数资料

| 型号: | ICS84326AMLF |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 150 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| 封装: | 7.50 X 15.33 MM, 2.30 MM HEIGHT, MS-013, MO-119, SOIC-24 |

| 文件页数: | 13/15页 |

| 文件大小: | 171K |

| 代理商: | ICS84326AMLF |

84326AM

www.icst.com/products/hiperclocks.html

REV. A MARCH 10, 2003

7

Integrated

Circuit

Systems, Inc.

ICS84326

CRYSTAL-TO-3.3V LVPECL

SERIAL ATTACHED SCSI CLOCK SYNTHESIZER/FANOUT BUFFER

PRELIMINARY

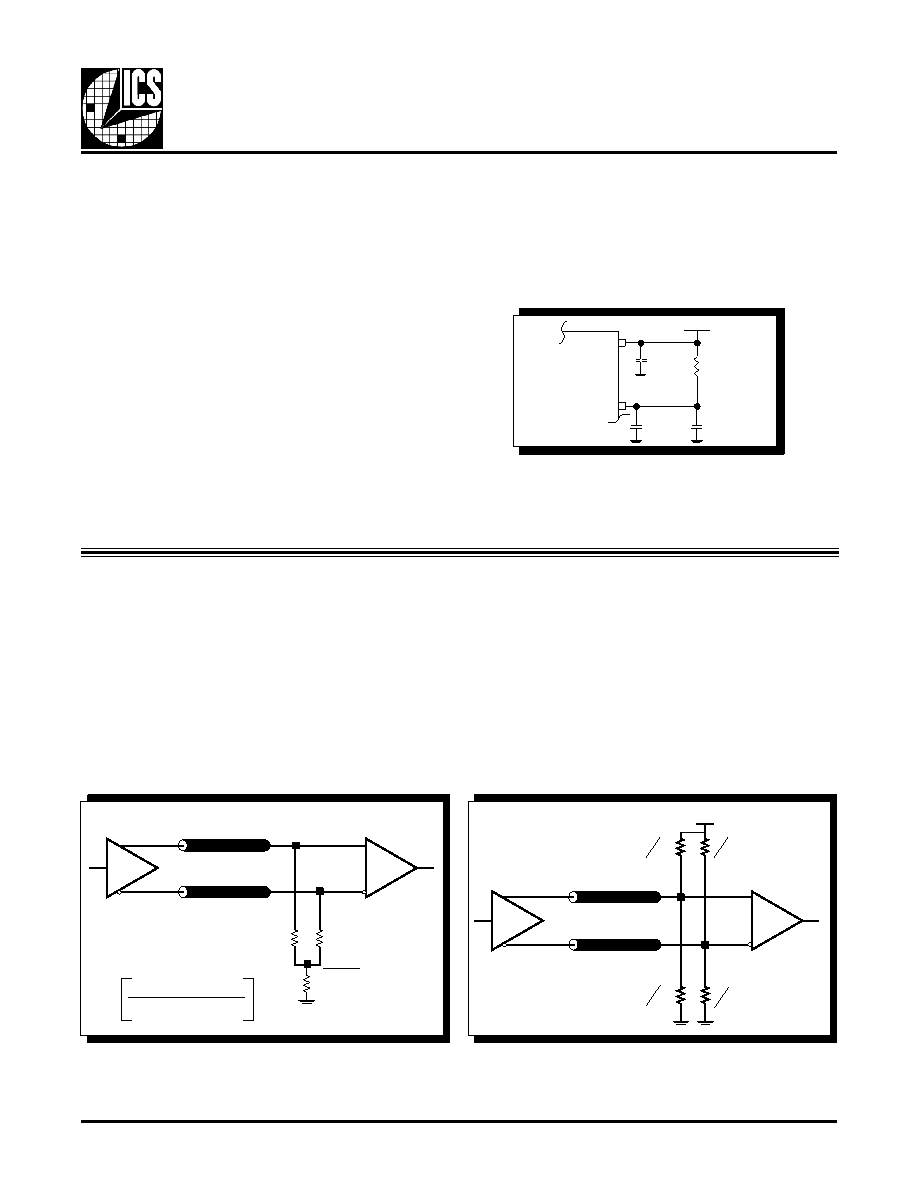

As in any high speed analog circuitry, the power supply pins

are vulnerable to random noise. The ICS84326 provides sepa-

rate power supplies to isolate any high switching

noise from the outputs to the internal PLL. V

CC, VCCA and VCCO

should be individually connected to the power supply plane

through vias, and bypass capacitors should be used for each

pin. To achieve optimum jitter performance, power supply iso-

lation is required.

Figure 1 illustrates how a 20

resistor along

with a 10

F and a .01F bypass capacitor should be con-

nected to each V

CCA pin.

POWER SUPPLY FILTERING TECHNIQUES

FIGURE 1. POWER SUPPLY FILTERING

20

V

CCA

10

F

.01

F

3.3V

.01

F

V

CC

APPLICATION INFORMATION

TERMINATION FOR 3.3V LVPECL OUTPUTS

The clock layout topology shown below is a typical termina-

tion for 3.3V LVPECL outputs. The two different layouts

mentioned are recommended only as guidelines.

FOUT and nFOUT are low impedance follower outputs that

generate ECL/LVPECL compatible outputs. Therefore, termi-

nating resistors (DC current path to ground) or current

sources must be used for functionality. These outputs are

FIGURE 2B. LVPECL OUTPUT TERMINATION

3.3V

F

OUT

F

IN

5

2 Zo

Z

o

5

2

Z

o

3

2

Z

o

3

2

Z

o = 50

Z

o = 50

FIGURE 2A. LVPECL OUTPUT TERMINATION

RTT =

1

(V

OH + VOL / VCC –2) –2

Z

o

Z

o = 50

Z

o = 50

50

50

RTT

V

CC - 2V

F

IN

F

OUT

designed to drive 50

transmission lines. Matched impedance

techniques should be used to maximize operating

frequency and minimize signal distortion.

Figures 2A and 2B

show two different layouts which are recommended only

as guidelines. Other suitable clock layouts may exist and it

would be recommended that the board designers simulate to

guarantee compatibility across all printed circuit and clock

component process variations.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS84327AM | 625 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS84329AVLF | 700 MHz, OTHER CLOCK GENERATOR, PQCC28 |

| ICS84329AVT | 700 MHz, OTHER CLOCK GENERATOR, PQCC28 |

| ICS84329AYT | 700 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS84329AVLFT | 700 MHz, OTHER CLOCK GENERATOR, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS84326AMT | 制造商:ICS 制造商全称:ICS 功能描述:CRYSTAL-TO-3.3V LVPECL SERIAL ATTACHED SCSI CLOCK SYNTHESIZER/FANOUT BUFFER |

| ICS84327 | 制造商:ICS 制造商全称:ICS 功能描述:CRYSTAL-TO-3.3V LVPECL FREQUENCY SYNTHESIZER W/INTEGRATED FANOUT BUFFER |

| ICS84327AM | 制造商:ICS 制造商全称:ICS 功能描述:CRYSTAL-TO-3.3V LVPECL FREQUENCY SYNTHESIZER W/INTEGRATED FANOUT BUFFER |

| ICS84327AMLF | 功能描述:IC SYNTHESIZER LVPECL 24SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS84327AMLFT | 功能描述:IC SYNTHESIZER LVPECL 24SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。