- 您现在的位置:买卖IC网 > PDF目录67691 > ICS8432DYI-01 700 MHz, OTHER CLOCK GENERATOR, PQFP32 PDF资料下载

参数资料

| 型号: | ICS8432DYI-01 |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 700 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| 封装: | 7 X 7 MM, 1.40 MM HEIGHT, MS-026, LQFP-32 |

| 文件页数: | 2/17页 |

| 文件大小: | 185K |

| 代理商: | ICS8432DYI-01 |

8432DYI-01

www.icst.com/products/hiperclocks.html

REV. B FEBRUARY 7, 2003

10

Integrated

Circuit

Systems, Inc.

ICS8432I-01

700MHZ, CRYSTAL-TO-3.3V DIFFERENTIAL

LVPECL FREQUENCY SYNTHESIZER

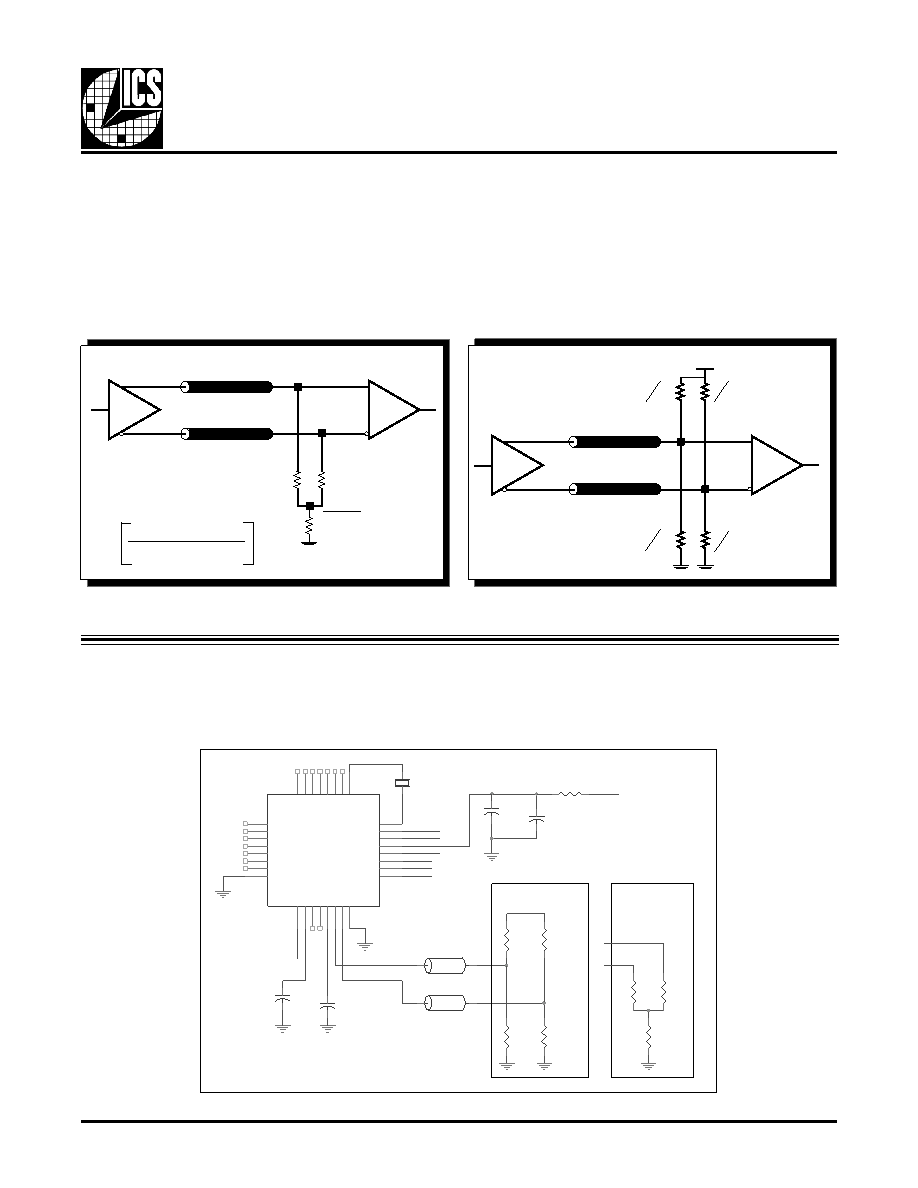

The clock layout topology shown below is a typical termina-

tion for LVPECL outputs. The two different layouts mentioned

are recommended only as guidelines.

FOUTx and nFOUTx are low impedance follower outputs that

generate ECL/LVPECL compatible outputs. Therefore, terminat-

ing resistors (DC current path to ground) or current sources

must be used for functionality. These outputs are designed to

FIGURE 4B. LVPECL OUTPUT TERMINATION

3.3V

F

OUT

F

IN

5

2 Zo

Z

o

5

2

Z

o

3

2

Z

o

3

2

Z

o = 50

Z

o = 50

FIGURE 4A. LVPECL OUTPUT TERMINATION

RTT =

1

(V

OH + VOL / VCC –2) –2

Z

o

Z

o = 50

Z

o = 50

50

50

RTT

V

CC - 2V

F

IN

F

OUT

drive 50

transmission lines. Matched impedance techniques

should be used to maximize operating frequency and minimize

signal distortion.

Figures 4A and 4B show two different layouts

which are recommended only as guidelines. Other suitable clock

layouts may exist and it would be recommended that the board

designers simulate to guarantee compatibility across all printed

circuit and clock component process variations.

XTAL_SEL

VCC

Termination A

REF_IN

MR

X1

FO

UTN

IN-

R7

10

R2

84

R3

125

IN-

R1

125

S_CLOCK

IN+

C14

0.1u

FO

UT

TEST

TL1

Zo = 50 Ohm

S_DATA

Termination

B (Not shown

in the layout)

C16

10u

R3

50

S_LOAD

VCC

C15

0.1u

R4

84

C11

0.01u

R2

50

R1

50

IN+

TL2

Zo = 50 Ohm

VCC

U1

8432-01

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

32

31

30

29

28

27

26

25

M5

M6

M7

M8

N0

N1

nc

VEE

TEST

VCC

FO

UT1

nF

O

U

T

1

VCCO

FO

UT0

nF

O

U

T

0

VEE

MR

S_CLOCK

S_DATA

S_LOAD

VCCA

nXTAL_SEL

REF_IN

XTAL1

M4

M3

M2

M1

M0

VCO_

SEL

nP

_LO

A

D

XTAL

2

FIGURE 5A. SCHEMATIC OF RECOMMENDED LAYOUT

TERMINATION FOR LVPECL OUTPUTS

LAYOUT GUIDELINE

The schematic of the ICS8432I-01 layout example used in

this layout guideline is shown in

Figure 5A. The ICS8432I-01

recommended PCB board layout for this example is shown in

Figure 5B. This layout example is used as a general guideline.

The layout in the actual system will depend on the selected

component types, the density of the components, the density

of the traces, and the stack up of the P.C. board.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8432DYI-01LF | 700 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS8432DYI-01LFT | 700 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| ICS8432DYI-101LFT | 8432 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS8432DYI-101LF | 8432 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS8432DYI-101T | 8432 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS8432DYI-101 | 制造商:ICS 制造商全称:ICS 功能描述:700MHZ, DIFFERENTIAL-TO-3.3V LVPECL FREQUENCY SYNTHESIZER |

| ICS8432DYI-101LF | 功能描述:IC SYNTHESIZER 700MHZ 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS8432DYI-101LFT | 功能描述:IC SYNTHESIZER 700MHZ 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS8432DYI-101T | 制造商:ICS 制造商全称:ICS 功能描述:700MHZ, DIFFERENTIAL-TO-3.3V LVPECL FREQUENCY SYNTHESIZER |

| ICS8432I-101 | 制造商:ICS 制造商全称:ICS 功能描述:700MHZ, DIFFERENTIAL-TO-3.3V LVPECL FREQUENCY SYNTHESIZER |

发布紧急采购,3分钟左右您将得到回复。