- 您现在的位置:买卖IC网 > PDF目录67695 > ICS8530DY (INTEGRATED DEVICE TECHNOLOGY INC) 8530 SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 PDF资料下载

参数资料

| 型号: | ICS8530DY |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 8530 SERIES, LOW SKEW CLOCK DRIVER, 16 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| 封装: | 7 X 7 MM, 1.40 MM HEIGHT, MS-026, LQFP-48 |

| 文件页数: | 10/13页 |

| 文件大小: | 251K |

| 代理商: | ICS8530DY |

8530DY

www.icst.com/products/hiperclocks.html

REV. E DECEMBER 2, 2003

6

Integrated

Circuit

Systems, Inc.

ICS8530

LOW SKEW, 1-TO-16

DIFFERENTIAL-TO-2.5V LVPECL FANOUT BUFFER

APPLICATION INFORMATION

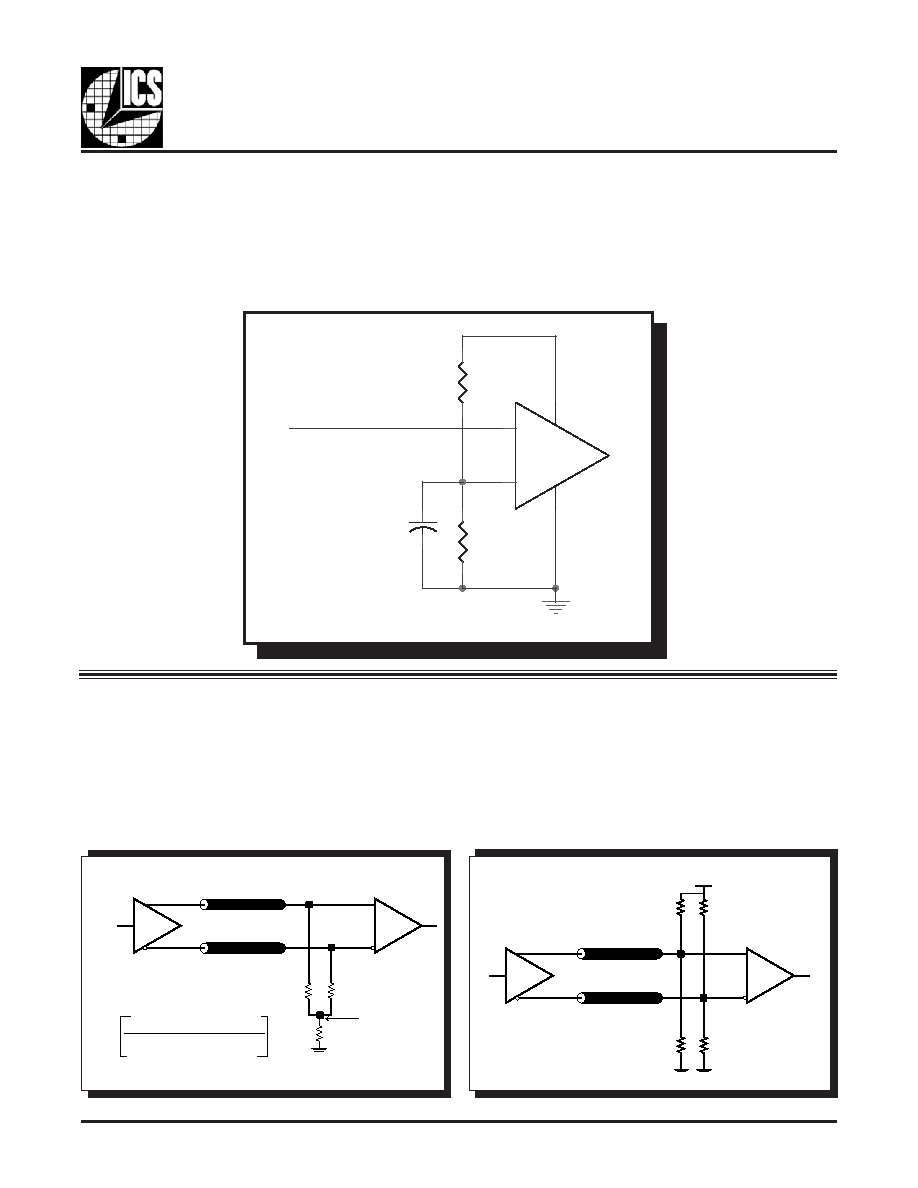

The clock layout topology shown below is a typical termina-

tion for LVPECL outputs. The two different layouts mentioned

are recommended only as guidelines.

FOUT and nFOUT are low impedance follower outputs that

generate ECL/LVPECL compatible outputs.Therefore, terminat-

ing resistors (DC current path to ground) or current sources

must be used for functionality. These outputs are designed to

drive 50

transmission lines. Matched impedance techniques

should be used to maximize operating frequency and minimize

signal distortion.

Figures 2A and 2B show two different layouts

which are recommended only as guidelines. Other suitable clock

layouts may exist and it would be recommended that the board

designers simulate to guarantee compatibility across all printed

circuit and clock component process variations.

TERMINATION FOR LVPECL OUTPUTS

FIGURE 1. SINGLE ENDED SIGNAL DRIVING DIFFERENTIAL INPUT

V

CC - 2V

50

50

RTT

Z

o = 50

Z

o = 50

FOUT

FIN

RTT =

Z

o

1

((V

OH + VOL) / (VCC – 2)) – 2

3.3V

125

125

84

84

Z

o = 50

Z

o = 50

FOUT

FIN

FIGURE 2B. LVPECL OUTPUT TERMINATION

FIGURE 2A. LVPECL OUTPUT TERMINATION

WIRING THE DIFFERENTIAL INPUT TO ACCEPT SINGLE ENDED LEVELS

Figure 1 shows how the differential input can be wired to accept

single ended levels. The reference voltage V_REF = V

CC/2 is

generated by the bias resistors R1, R2 and C1. This bias circuit

should be located as close as possible to the input pin. The ratio

of R1 and R2 might need to be adjusted to position the V_REF in

the center of the input voltage swing. For example, if the input

clock swing is only 2.5V and V

CC = 3.3V, V_REF should be 1.25V

and R2/R1 = 0.609.

V_REF

R1

1K

C1

0.1u

R2

1K

Single Ended Clock Input

CLK

nCLK

VCC

相关PDF资料 |

PDF描述 |

|---|---|

| ICS85310AY-01LFT | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS85310AY-01LF | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS85310AY-01 | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS85310AY-11LF | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS85310AY-11T | LOW SKEW CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS8530DY01 | 制造商:ICS 功能描述: |

| ICS8530DY-01LF | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 产品培训模块:High Bandwidth Product Overview 标准包装:1,000 系列:Precision Edge® 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:4 差分 - 输入:输出:是/是 输入:CML,LVDS,LVPECL 输出:CML 频率 - 最大:2.5GHz 电源电压:2.375 V ~ 2.625 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) |

| ICS8530DY-01LFT | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS8530DYI-01LF | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS8530DYI-01LFT | 功能描述:IC CLK BUFF 1:16 500MHZ 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。