- 您现在的位置:买卖IC网 > PDF目录8712 > ICS854105AGLFT (IDT, Integrated Device Technology Inc)IC CLK BUFF 1:4 250MHZ 16-TSSOP PDF资料下载

参数资料

| 型号: | ICS854105AGLFT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 8/12页 |

| 文件大小: | 0K |

| 描述: | IC CLK BUFF 1:4 250MHZ 16-TSSOP |

| 标准包装: | 2,500 |

| 系列: | HiPerClockS™ |

| 类型: | 扇出缓冲器(分配) |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:4 |

| 差分 - 输入:输出: | 无/是 |

| 输入: | LVCMOS,LVTTL |

| 输出: | LVDS |

| 频率 - 最大: | 250MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 带卷 (TR) |

| 其它名称: | 854105AGLFT |

ICS854105 Data Sheet

LOW SKEW, 1-TO-4, LVCMOS/LVTTL-TO-LVDS FANOUT BUFFER

ICS854105AG REVISION A FEBRUARY 23, 2010

5

2010 Integrated Device Technology, Inc.

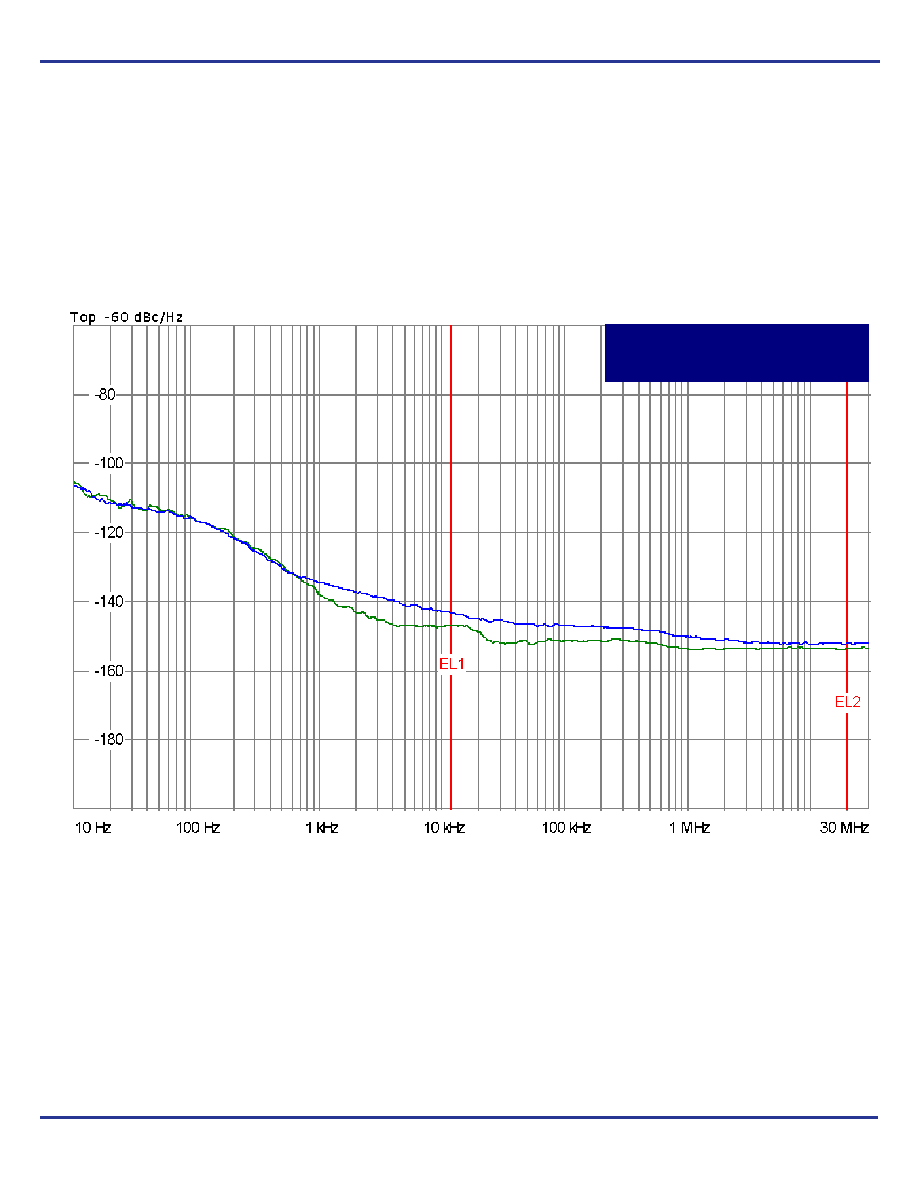

Additive Phase Jitter

The spectral purity in a band at a specific offset from the fundamental

compared to the power of the fundamental is called the dBc Phase

Noise. This value is normally expressed using a Phase noise plot

and is most often the specified plot in many applications. Phase noise

is defined as the ratio of the noise power present in a 1Hz band at a

specified offset from the fundamental frequency to the power value of

the fundamental. This ratio is expressed in decibels (dBm) or a ratio

of the power in the 1Hz band to the power in the fundamental. When

the required offset is specified, the phase noise is called a dBc value,

which simply means dBm at a specified offset from the fundamental.

By investigating jitter in the frequency domain, we get a better

understanding of its effects on the desired application over the entire

time record of the signal. It is mathematically possible to calculate an

expected bit error rate given a phase noise plot.

As with most timing specifications, phase noise measurements has

issues relating to the limitations of the equipment. Often the noise

floor of the equipment is higher than the noise floor of the device. This

is illustrated above. The device meets the noise floor of what is

shown, but can actually be lower. The phase noise is dependent on

the input source and measurement equipment.

The source generator "Rohde & Schwarz SMA100 Signal Generator

as external input to an Agilent 8133A 3GHz Pulse Generator".

Additive Phase Jitter @ 155.52MHz

12kHz to 20MHz = 0.16ps (typical)

SSB

Phas

e

N

o

ise

dBc/Hz

Offset from Carrier Frequency (Hz)

相关PDF资料 |

PDF描述 |

|---|---|

| V72A24H400BG2 | CONVERTER MOD DC/DC 24V 400W |

| V72A24H400BF3 | CONVERTER MOD DC/DC 24V 400W |

| V72A24H400BF2 | CONVERTER MOD DC/DC 24V 400W |

| IDT5V2310PGG | IC CLK BUFF 1:10 200MHZ 24-TSSOP |

| V72A24H400BF | CONVERTER MOD DC/DC 24V 400W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS854110AKILF | 功能描述:IC CLOCK BUFFER MUX 2:10 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS854110AKILFT | 功能描述:IC CLOCK BUFFER MUX 2:10 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS854110AYILF | 功能描述:IC CLOCK BUFFER MUX 2:10 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS854110AYILFT | 功能描述:IC CLOCK BUFFER MUX 2:10 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS85411AMILF | 功能描述:IC CLOCK BUFFER 1:2 650MHZ 8SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 产品培训模块:High Bandwidth Product Overview 标准包装:1,000 系列:Precision Edge® 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:4 差分 - 输入:输出:是/是 输入:CML,LVDS,LVPECL 输出:CML 频率 - 最大:2.5GHz 电源电压:2.375 V ~ 2.625 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。