- 您现在的位置:买卖IC网 > PDF目录67698 > ICS8546AG-01LF 266 MHz, OTHER CLOCK GENERATOR, PDSO24 PDF资料下载

参数资料

| 型号: | ICS8546AG-01LF |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 266 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| 封装: | 4.40 X 7.80 MM, 0.92 MM HEIGHT, ROHS COMPLIANT, TSSOP-24 |

| 文件页数: | 2/13页 |

| 文件大小: | 622K |

| 代理商: | ICS8546AG-01LF |

8546AG-01

www.icst.com/products/hiperclocks.html

REV. A AUGUST 24, 2005

10

Integrated

Circuit

Systems, Inc.

ICS8546-01

LOW SKEW, 1-TO-6, CRYSTAL OSCILLATOR-TO-

LVDS FANOUT BUFFER

PRELIMINARY

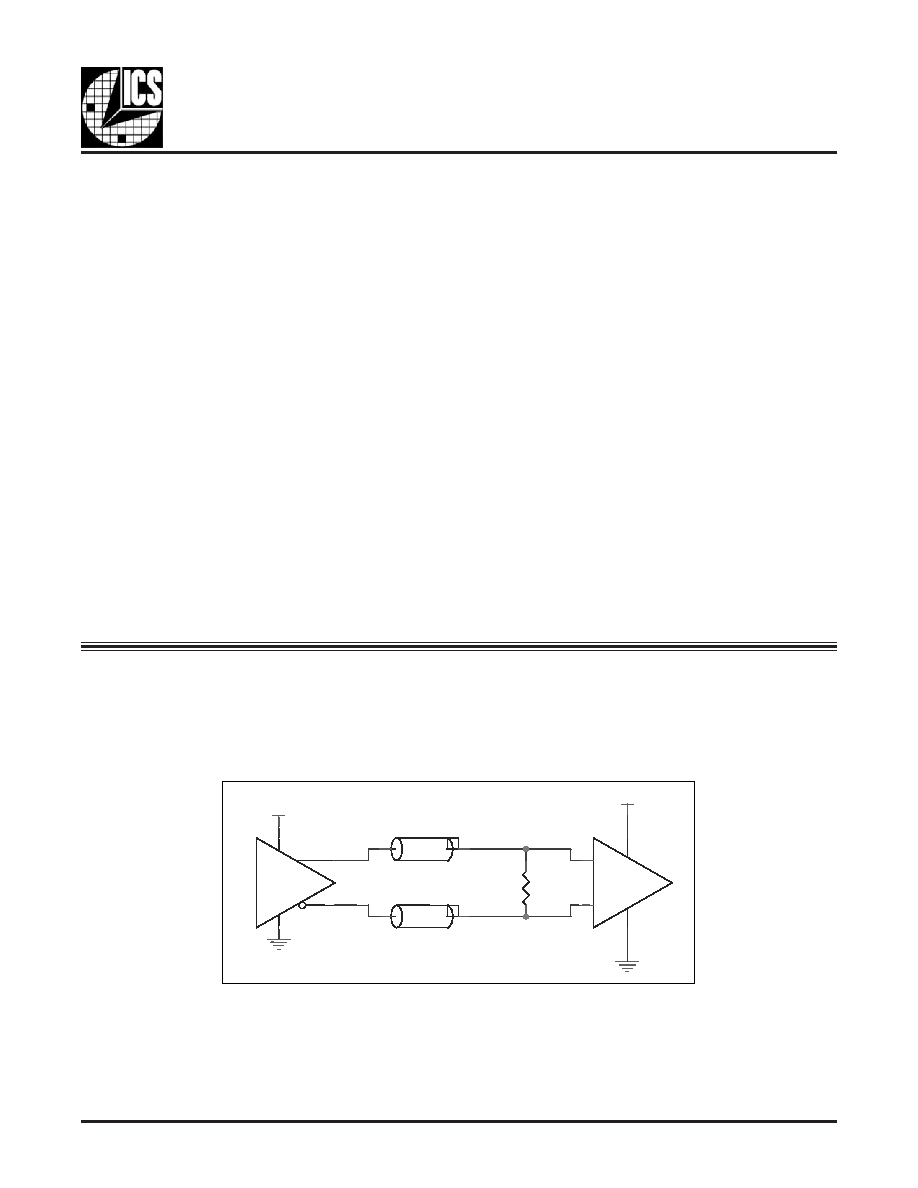

3.3V, 2.5V LVDS DRIVER TERMINATION

A general LVDS interface is shown in Figure 4. In a 100

Ω

differential transmission line environment, LVDS drivers

require a matched load termination of 100

Ω across near

FIGURE 4. TYPICAL LVDS DRIVER TERMINATION

the receiver input. For a multiple LVDS outputs buffer, if only

partial outputs are used, it is recommended to terminate the

un-used outputs.

R1

100

3.3V or 2.5V

100

Ω Differential Transmission

VDD

+

-

LVDS

INPUTS:

CRYSTAL INPUT:

For applications not requiring the use of the crystal oscillator

input, both XTAL_IN and XTAL_OUT can be left floating.

Though not required, but for additional protection, a 1k

Ω

resistor can be tied from XTAL_IN to ground.

CLK INPUT:

For applications not requiring the use of the test clock, it can

be left floating. Though not required, but for additional

protection, a 1k

Ω resistor can be tied from the CLK input to

ground.

CLK/nCLK INPUT:

For applications not requiring the use of the differential input,

both CLK and nCLK can be left floating. Though not required,

but for additional protection, a 1k

Ω resistor can be tied from

CLK to ground.

LVCMOS CONTROL PINS:

All control pins have internal pull-ups or pull-downs; additional

resistance is not required but can be added for additional

protection. A 1k

Ω resistor can be used.

RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

OUTPUTS:

LVDS OUTPUT

All unused LVDS outputs can be left floating. We recommend

that there is no trace attached. Both sides of the differential

output pair should either be left floating or terminated.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8547AYT | LOW SKEW CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8547AY | LOW SKEW CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS8547AYLF | LOW SKEW CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS854S006IT | 854S SERIES, LOW SKEW CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| ICS854S013ILFT | 854S SERIES, LOW SKEW CLOCK DRIVER, 3 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS8546AG-01LFT | 功能描述:IC CLOCK BUFFER MUX 3:6 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS8547AY | 功能描述:IC CLK BUFFER 1:2 700MHZ 48-LQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS854S006AGILF | 功能描述:IC CLK BUFFER 1:6 1.7GHZ 24TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS854S006AGILFT | 功能描述:IC CLK BUFF 1:6 1.7GHZ 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS854S015CKI-01LF | 制造商:Integrated Device Technology Inc 功能描述:IC FANOUT BUFFER 24VFQFN |

发布紧急采购,3分钟左右您将得到回复。