- 您现在的位置:买卖IC网 > PDF目录67702 > ICS873991AYLF 873991 SERIES, PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 PDF资料下载

参数资料

| 型号: | ICS873991AYLF |

| 元件分类: | 时钟及定时 |

| 英文描述: | 873991 SERIES, PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, MS-026, LQFP-52 |

| 文件页数: | 1/17页 |

| 文件大小: | 171K |

| 代理商: | ICS873991AYLF |

873991AY

www.icst.com/products/hiperclocks.html

REV. A JUNE 13, 2005

1

Integrated

Circuit

Systems, Inc.

ICS873991

LOW VOLTAGE, LVCMOS/

LVPECL-TO-LVPECL/ECL CLOCK GENERATOR

GENERAL DESCRIPTION

The ICS873991 is a low voltage, low skew, 3.3V

LVPECL or ECL Clock Generator and a member of

the HiPerClockS family of High Performance

Clock Solutions from ICS. The ICS873991 has two

selectable clock inputs. The PCLK, nPCLK pair can

accept an LVPECL input and the TEST_CLK pin can accept a

LVCMOS or LVTTL input. This device has a fully integrated PLL

along with frequency configurable outputs. An external feedback

input and output regenerates clocks with “zero delay”.

The four independent banks of outputs each have their own out-

put dividers, which allow the device to generate a multitude of

different bank frequency ratios and output-to-input frequency ra-

tios. The output frequency range is 25MHz to 400MHz and the

input frequency range is 6.25MHz to 125MHz. The PLL_SEL in-

put can be used to bypass the PLL for test and system debug

purposes. In bypass mode, the input clock is routed around the

PLL and into the internal output dividers.

The ICS873991 also has a SYNC output which can be used for

system synchronization purposes. It monitors Bank A and Bank

C outputs for coincident rising edges and signals a pulse per the

timing diagrams in this data sheet.This feature is used primarily

in applications where Bank A and Bank C are running at different

frequencies, and is particularly useful when they are running at

non-integer multiples of each other.

Example Applications:

1. Line Card Multiplier: Multiply 19.44MHz from a back-plane

to 77.76MHz on the line card ASIC and Serdes.

2. Zero Delay Buffer: Fan out up to thirteen 100MHz copies

from a reference clock to multiple processing units on an

embedded system.

FEATURES

14 differential LVPECL outputs

Selectable differential LVPECL or TEST_CLK inputs

PCLK, nPCLK can accept the following input levels:

LVPECL, CML, SSTL

TEST_CLK accepts the following input levels:

LVCMOS, LVTTL

Input frequency range: 6.25MHz to 125MHz

Output frequency: 400MHz (maximum)

VCO range: 200MHz to 800MHz

Output skew: 250ps (maximum)

Cycle-to-cyle jitter: ±50ps (typical)

LVPECL mode operating voltage supply range:

V

CC = 3.135V to 3.465V, VEE = 0V

ECL mode operating voltage supply range:

V

CC = 0V, VEE = -3.465V to -3.135V

0°C to 70°C ambient operating temperature

Industrial temperature available upon request

Lead-Free package fully RoHS compliant

HiPerClockS

ICS

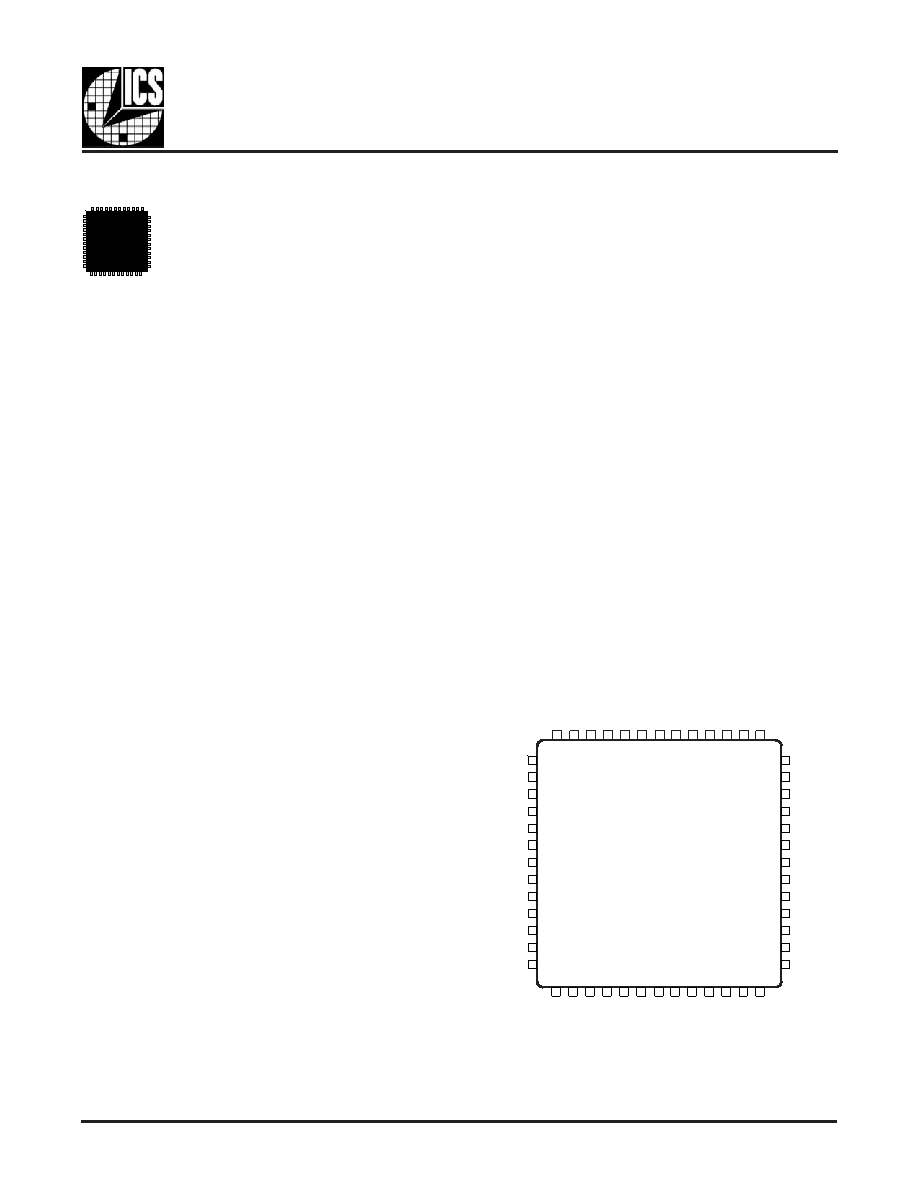

PIN ASSIGNMENT

V

EE

MR

PLL_EN

REF_SEL

FSEL_FB2

FSEL_FB1

FSEL_FB0

TEST_CLK

PCLK

nPCLK

V

CC

EXT_FB

nEXT_FB

nQB3

QB3

VCCO

nQA0

QA0

nQA1

QA1

nQA2

QA2

nQA3

QA3

SYNC_SEL

VCO_SEL

40

41

42

43

44

45

46

47

48

49

50

51

52

1

2

3

4

5

6

7

8

9 10 11 12 13

26

25

24

23

22

21

20

19

18

17

16

15

14

39 38 37 36 35 34 33 32 31 30 29 28 27

QC1

nQC1

QC0

nQC0

VCCO

QD1

nQD1

QD0

nQD0

VCCO

QFB

nQFB

VCCA

FSEL0

QB2

nQB2

FSEL1

QB1

nQB1

FSEL2

QB0

nQB0

V

CCO

QC2

nQC2

FSEL3

ICS873991

52-Lead LQFP

10mm x 10mm x 1.4mm package body

Y package

Top View

相关PDF资料 |

PDF描述 |

|---|---|

| ICS873995AYLF | 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873995AYT | 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873995AY | 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873995AYLFT | 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873996AYLFT | 873996 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS873991AYLFT | 功能描述:IC CLK GEN LV LVPECL 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873995AYLF | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873995AYLFT | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873996AYLF | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ICS873996AYLFT | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。