- 您现在的位置:买卖IC网 > PDF目录67702 > ICS873995AY 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 PDF资料下载

参数资料

| 型号: | ICS873995AY |

| 元件分类: | 时钟及定时 |

| 英文描述: | 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| 封装: | 7 X 7 MM, 1 MM HEIGHT, MS-026, TQFP-48 |

| 文件页数: | 1/16页 |

| 文件大小: | 239K |

| 代理商: | ICS873995AY |

873995AY

www.icst.com/products/hiperclocks.html

REV. A APRIL 12, 2006

1

Integrated

Circuit

Systems, Inc.

ICS873995

DIFFERENTIAL-TO-3.3V LVPECL

ZERO DELAY/MULTIPLIER/DIVIDER

PRELIMINARY

GENERAL DESCRIPTION

The ICS873995 is a Zero Delay/Multiplier/Divider

with hitless input clock switching capability and a

member of the HiPerClockS family of low jitter/

phase noise devices from ICS. The ICS873995 is

ideal for use in redundant, fault tolerant clock trees

where low phase noise and low jitter are critical. The device

receives two differential LVPECL clock signals from which it

generates 6 LVPECL clock outputs with “zero” delay.The output

divider and feedback divider selections also allow for frequency

multiplication or division.

The ICS873995 Dynamic Clock Switch (DCS) circuit

continuously monitors both input clock signals. Upon detection

of a failure (input clock stuck LOW or HIGH for at least 1 period),

INP_BAD for that clock will be set HIGH. If that clock is the

primary clock, the DCS will switch to the good secondary

clock and phase/frequency alignment will occur with minimal

output phase disturbance.

The low jitter characteristics combined with input clock monitor-

ing and automatic switching from bad to good input clocks make

the ICS873995 an ideal choice for mission critical applications that

utilize 1G or 10G Ethernet or 1G/4G/10G Fibre Channel.

HiPerClockS

ICS

FEATURES

Six differential 3.3V LVPECL outputs

Selectable differential clock inputs

CLKx, nCLKx pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

Input clock frequency range: 49MHz to 213.33MHz

Output clock frequency range: 49MHz to 640MHz

VCO range: 490MHz to 640MHz

External feedback for “zero delay” clock regeneration

with configurable frequencies

Output skew: 70ps (maximum) (design target)

RMS phase jitter (1.875MHz - 20MHz): <1ps (design

target) assuming a low phase noise reference clock input

3.3V supply voltage

0°C to 70°C ambient operating temperature

Available in both standard and lead-free RoHS compliant

packages

nMR

NA[2:0]

000 ÷1

001 ÷2

010 ÷3

011 ÷4

100 ÷5

101 ÷6

110 ÷8

111 ÷10(default)

NB[2:0]

000 ÷1

001 ÷2

010 ÷3

011 ÷4

100 ÷5

101 ÷6

110 ÷8

111 ÷10(default)

NFB[2:0]

000 Reserved

001 Reserved

010 ÷3

011 ÷4

100 ÷5

101 ÷6

110 ÷8

111 ÷10(default)

nMR

Dynamic Switch

Logic

Phase

Detector

0

1

VCO

490MHz - 640MHz

3

0

1

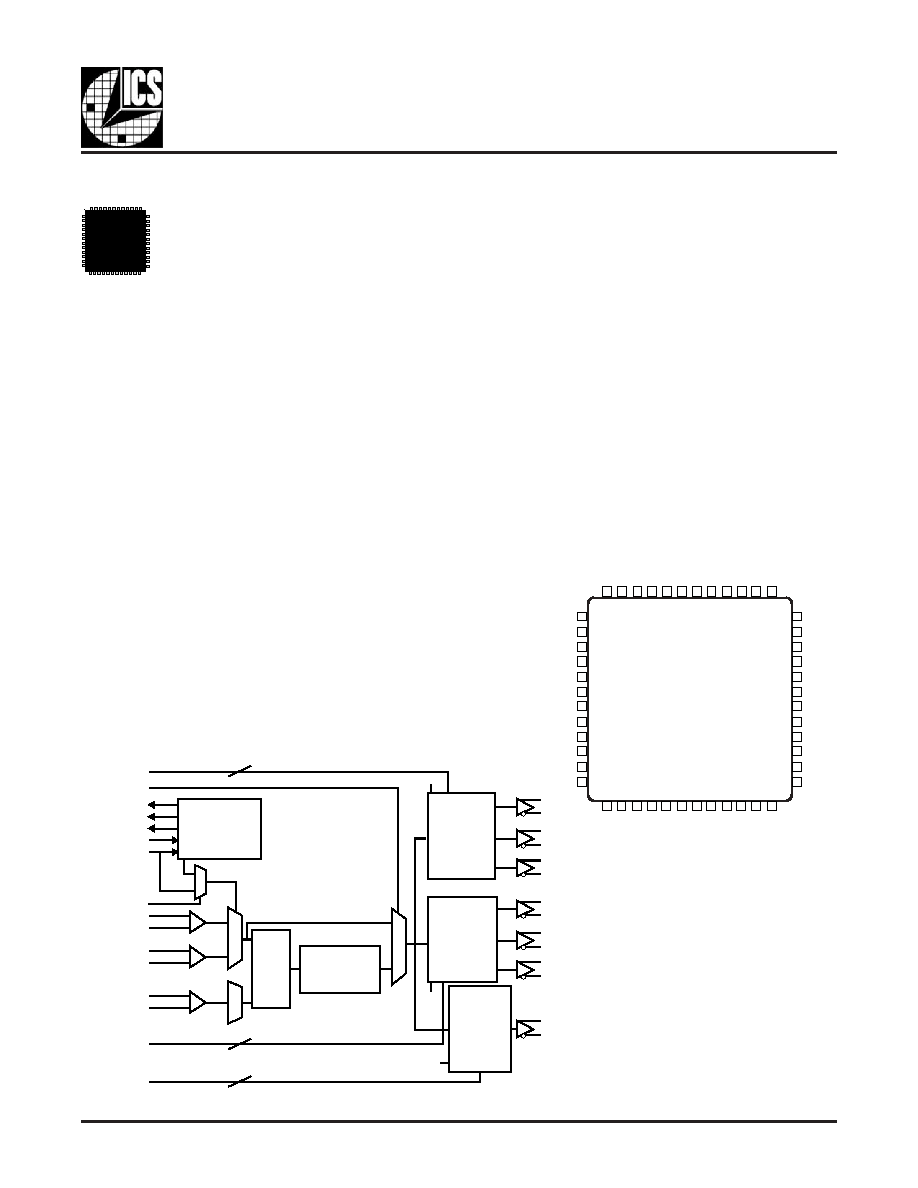

PIN ASSIGNMENT

V

CC

NB0

NB1

NB2

V

EE

NA0

NA1

NA2

V

CCO

_

B

nQB2

QB2

nQB1

48 47 46 45 44 43 42 41 40 39 38 37

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

PLL_SEL

nMR

nINIT

VEE

CLK0

nCLK0

CLK1

nCLK1

EXT_FB

nEXT_FB

SEL_CLK

VEE

VCCO_A

QA0

nQA0

QA1

nQA1

QA2

nQA2

VCCO_A

VCCO_B

QB0

nQB0

QB1

MAN_OVERRIDE

V

CC

INP1BAD

INP0BAD

CLK_SELECTED

NFB2

NFB1

NFB0

V

CCA

nQFB

QFB

V

CCO

_

FB

48-Lead TQFP, E-Pad

7mm x 7mm x 1.0mm

package body

Y Package

Top View

ICS873995

NA[2:0]

PLL_SEL

CLK_SELECTED

INP1BAD

INP0BAD

nINIT

SEL_CLK

MAN_OVERRIDE

CLK0

nCLK0

CLK1

nCLK1

EXT_FB

nEXT_FB

NB[2:0]

NFB[2:0]

QA0

nQA0

QA1

nQA1

QA2

nQA2

QB0

nQB0

QB1

nQB1

QB2

nQB2

QFB

nQFB

BLOCK DIAGRAM

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS873995AYLFT | 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873996AYLFT | 873996 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873996AYT | 873996 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873996AY | 873996 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| ICS873996AYLFT | 873996 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS873995AYLF | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873995AYLFT | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS873996AYLF | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ICS873996AYLFT | 功能描述:IC ZD/MULT/DIVIDER 48-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS874001AGI-02LF | 功能描述:IC PCI EXPRSS/JITT ATTEN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FemtoClock™, PCI Express™ (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。