- 您现在的位置:买卖IC网 > PDF目录67702 > ICS8745BM-21LFT (INTEGRATED DEVICE TECHNOLOGY INC) 8745 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 PDF资料下载

参数资料

| 型号: | ICS8745BM-21LFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 8745 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 封装: | 7.50 X 12.80 MM, 2.30 MM HEIGHT, ROHS COMPLIANT, MS-013, MO-119, SOIC-20 |

| 文件页数: | 12/19页 |

| 文件大小: | 840K |

| 代理商: | ICS8745BM-21LFT |

ICS8745B-21

1:1 DIFFERENTIAL-TO-LVDS ZERO DELAY CLOCK GENERATOR

IDT / ICS LVDS ZERO DELAY CLOCK GENERATOR

2

ICS8745BM-21REV. C APRIL 17, 2007

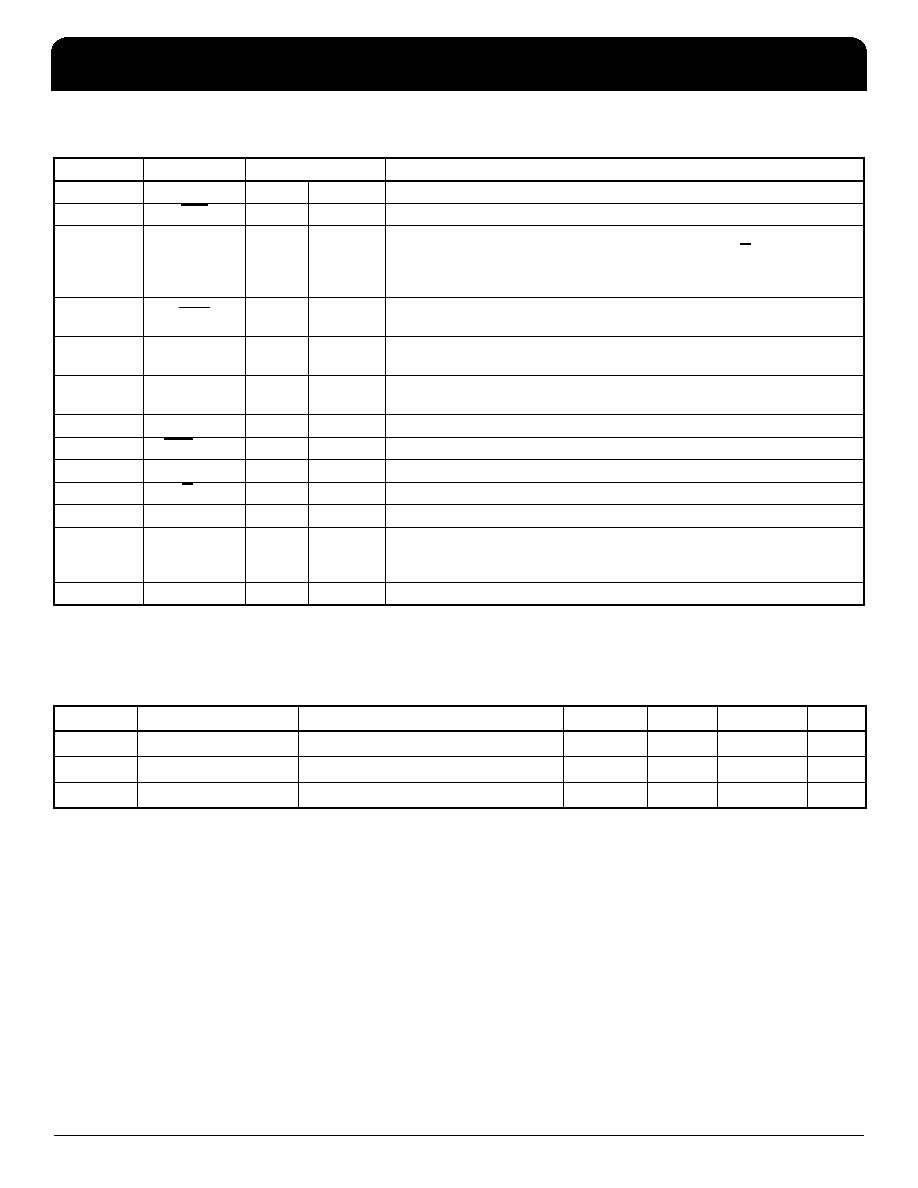

Table 1. Pin Descriptions

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

Table 2. Pin Characteristics

Number

Name

Type

Description

1

CLK

Input

Pulldown

Non-inverting differential clock input.

2CLK

Input

Pullup

Inverting differential clock input.

3

MR

Input

Pulldown

Active HIGH Master Reset. When logic HIGH, the internal dividers are reset

causing the true output Q to go low and the inverted output Q to go high. When

logic LOW, the internal dividers and the outputs are enabled.

LVCMOS / LVTTL interface levels.

4FBIN

Input

Pullup

Inverting differential feedback input to phase detector for regenerating clocks

with “Zero Delay.”

5

FBIN

Input

Pulldown

Non-inverted differential feedback input to phase detector for regenerating

clocks with “Zero Delay.”

6, 15,

19, 20

SEL2, SEL3,

SEL0 SEL1

Input

Pulldown

Determines output divider values in Table 3. LVCMOS / LVTTL interface levels.

7, 11

VDDO

Power

Output supply pins.

8, 9

QFB/QFB

Output

Differential feedback output pair. LVDS interface levels.

10, 14

GND

Power

Power supply ground.

12, 13

Q/Q

Output

Differential output pair. LVDS interface levels.

16

VDDA

Power

Analog supply pin.

17

PLL_SEL

Input

Pullup

PLL select. Selects between the PLL and reference clock as the input to the

dividers. When LOW, selects reference clock.

LVCMOS/LVTTL interface levels.

18

VDD

Power

Core supply pin.

Symbol

Parameter

Test Conditions

Minimum

Typical

Maximum

Units

CIN

Input Capacitance

4

pF

RPULLUP

Input Pullup Resistor

51

kΩ

RPULLDOWN Input Pulldown Resistor

51

kΩ

相关PDF资料 |

PDF描述 |

|---|---|

| ICS8745BM-21LF | 8745 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| ICS8745BM-21T | 8745 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| ICS8745BMI-21LF | 8745 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| ICS8745BMI-21 | 8745 SERIES, PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| ICS8745BMI-21LF | PLL BASED CLOCK DRIVER, 1 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS8745BMI-21LF | 功能描述:IC CLK GEN 1:1 DIFF-LVDS 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ICS8745BMI-21LFT | 功能描述:IC CLK GEN 1:1 DIFF-LVDS 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS8745BY | 制造商:ICS 功能描述: 制造商:Integrated Device Technology Inc 功能描述: 制造商:Integrated Device Technology Inc 功能描述:8745 SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP32 |

| ICS8745BYI | 制造商:Integrated Device Technology Inc 功能描述: |

| ICS8745BYILF | 功能描述:IC CLK GEN 5LVDS 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

发布紧急采购,3分钟左右您将得到回复。