- 您现在的位置:买卖IC网 > PDF目录1999 > ICS894D115BGI-01LF (IDT, Integrated Device Technology Inc)IC CLK/DATA RECOVERY 20-TSSOP PDF资料下载

参数资料

| 型号: | ICS894D115BGI-01LF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 9/16页 |

| 文件大小: | 0K |

| 描述: | IC CLK/DATA RECOVERY 20-TSSOP |

| 标准包装: | 74 |

| 系列: | HiPerClockS™ |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | STM-1,STM-4 |

| 输入: | LVPECL |

| 输出: | LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 622.08MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

| 其它名称: | 894D115BGI-01LF |

ICS894D115I-01

OC-12/STM-4 AND OC-3/STM-1 CLOCK/DATA RECOVERY DEVICE

IDT / ICS CLOCK/DATA RECOVERY DEVICE

2

ICS894D115BGI-01 REV. C OCTOBER 15, 2008

Functional Description

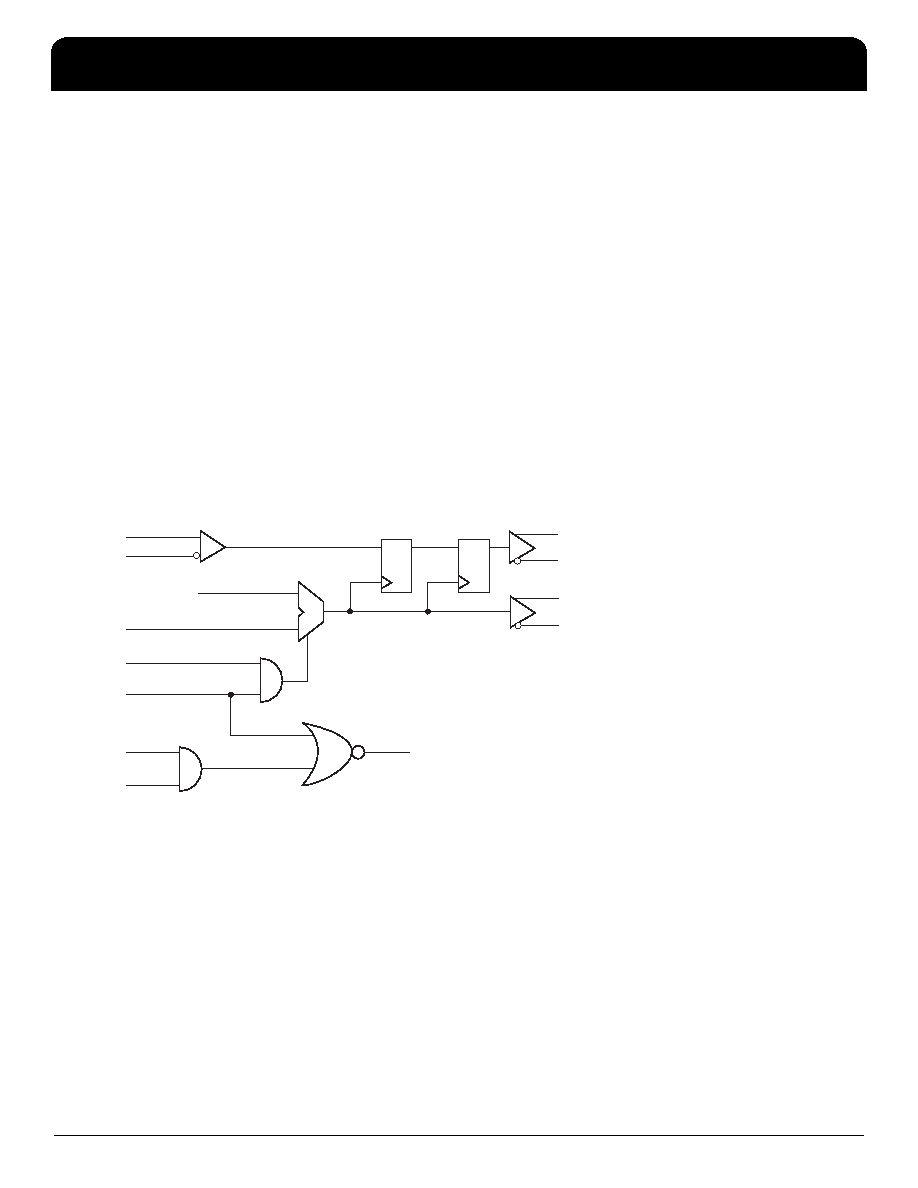

The ICS894D115I-01 is designed to extract the clock from a

NRZ-coded STM-4 (OC-12/STS-12) or STM-1 (OC-3/STS-3) input

data signal. The output signals are the recovered clock and retimed

data signal. The device contains an integrated PLL for clock

generation and to lock the output clock to the input data stream.

The PLL attempts to lock to the reference clock input (REF_CLK)

in absence of the serial data stream or if it is forced to by the control

inputs LOCK_REFN or SD. The output clock frequency is

controlled by the STS12 input. The output frequency is 622.08MHz

in STM-4/OC-12/STS-12 mode and 155.52MHz in

STM-1/OC-3/STS-3 mode.

The ICS894D115I-01 will maintain an output (CLK_OUT/

nCLK_OUT) frequency deviation of less than ±500ppm with

respect to the REF_CLK reference frequency in a loss of signal

state (LOS). During the LOS state, DATA_OUT is held at logic LOW

state and nDATA_OUT is held at logic HIGH state. An LOS state of

the ICS894D115I-01 is given when BYPASS is set to the logic

LOW state and either one of the SD or LOCK_REFN inputs are at

a logic LOW state. This will enable the use of the SD (signal detect)

and the LOCK_REFN (lock-to-reference) inputs to accept loss of

signal status information from electro-optical receivers. Please

refer to Figure 1, “Signal Detect/PLL Bypass Operation Control

Diagram”, for details.

The lock detect output (LOCK_DET) can be used to monitor the

operating state of the clock/data recovery circuit. LOCK_DET is set

to logic LOW level when the internal oscillator of the PLL and the

reference clock (REF_CLK) deviate from each other by more than

500ppm, or when the CDR is forced to lock the REF_CLK input by

the LOCK_REFN or SD control input. LOCK_DET is set to HIGH

when the PLL is locked to the input data stream and indicates valid

clock and data output signals.

The BYPASS pin should be set to logic LOW state in all

applications. BYPASS set to logic HIGH state is used during

factory test. In BYPASS mode (BYPASS and STS12 are at logic

HIGH state), the internal PLL is bypassed and the inverted

REF_CLK input signal is output at CLK_OUT/nCLK_OUT.

Figure 1. Signal Detect/PLL BYPASS Operation Control Diagram

LOS

(on-chip)

DATA_OUT

nDATA_OUT

CLK_OUT

nCLK_OUT

STS12

BYPASS

DATA_IN

nDATA_IN

PLL Clock

(on-chip)

SD

LOCK_REFN

REF_CLK

0

1

Pullup/Pulldown

Pulldown

Pullup

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9112AM-17LF | IC BUFFER HI PERFORMANCE 16-SOIC |

| ICS91305AMILF | IC CLOCK DRIVER LO JITTER 8-SOIC |

| ICS91305AMLF | IC CLOCK DRIVER LO JITTER 8-SOIC |

| ICS91309AGILF | IC CLK BUFFER ZD PLL 16TSSOP |

| ICS9161A-01CW16T | IC FREQUENCY GENERATOR 16-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS894D115BGI-01LFT | 功能描述:IC CLK/DATA RECOVERY 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS894D115BGI-01T | 功能描述:IC CLK/DATA RECOVERY 20-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS8S58035AKILF | 功能描述:IC CLOCK BUFFER MUX 2:6 32-VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS8S58035AKILFT | 功能描述:IC CLOCK BUFFER MUX 2:6 32-VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:HiPerClockS™ 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS8S73034AGILF | 制造商:Integrated Device Technology Inc 功能描述:IC DIVIDER LVPECL 16-TSSOP |

发布紧急采购,3分钟左右您将得到回复。