- 您现在的位置:买卖IC网 > PDF目录61073 > ICS9147F-09 83.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF资料下载

参数资料

| 型号: | ICS9147F-09 |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 83.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封装: | SSOP-48 |

| 文件页数: | 5/9页 |

| 文件大小: | 580K |

| 代理商: | ICS9147F-09 |

5

ICS9147-09

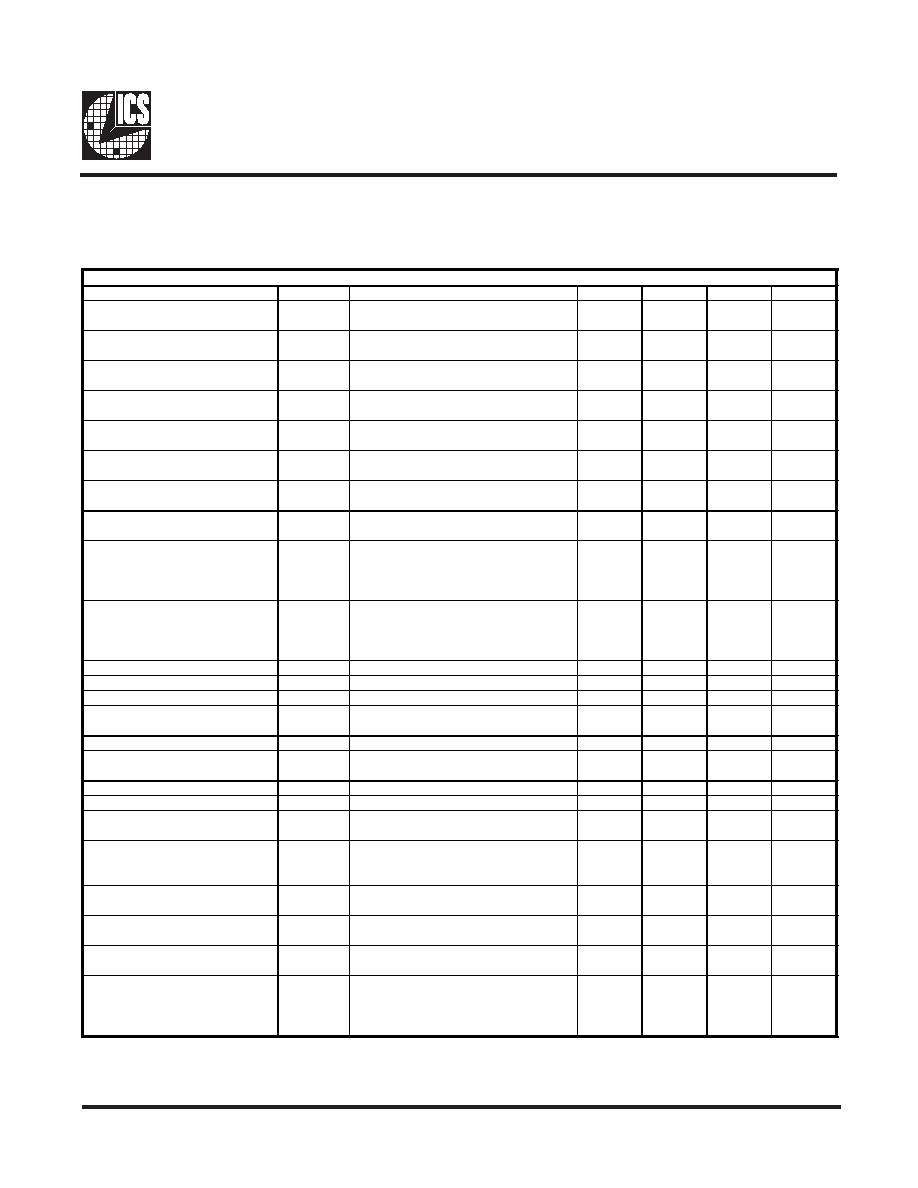

Electrical Characteristics at 3.3V

VDD = 3.0 3.7V, TA = 0 70

° C unless otherwise stated

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

AC Characteristics

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Rise Time

1

Tr1

20pF load, 0.8 to 2.0V

CPU, SDRAM, BUS & REF

-0.9

1.5

ns

Fall Time

1

Tf1

20pF load, 2.0 to 0.8V

CPU, SDRAM, BUS & REF

-0.8

1.4

ns

Rise Time

1

Tr3

20pF load, 0.8 to 2.0V

fixed 20 & 48 clocks

-0.9

1.5

ns

Fall Time

1

Tf3

20pF load, 2.0 to 0.8V

fixed 20 & 48 clocks

-1.1

1.5

ns

Rise Time

1

Tr4

20pF load, 0.4 to 2.0V , CPUL with

VDDL = 2.5V

-2.0

2.5

ns

Fall Time

1

Tf4

20pF load, 2.0 to 0.4V, CPUL with

VDDL = 2.5V

-1.6

2.5

ns

Duty Cycle

1

Dt

20pF load @ VOUT=1.4V

All clocks except 48MHz and REF

47

52

57

%

Duty Cycle1

DT2

20pF load @ VOUT=1.4V

48MHz and REF outputs

40

50

60

%

Jitter, One Sigma1

Tjis1

CPU & BUS Clocks; Load=20pF,

SDRAM; Load = 30pF, VDDL = 3.3

or 2.5V

FOUT=25 MHz, BSEL=1

-50

150

ps

Jitter, Absolute

1

Tjab1

CPU & BUS Clocks; Load=20pF,

SDRAM; Load = 30pF, VDDL = 3.3

or 2.5V

FOUT

≥25 MHz, BSEL=1

-250

-

250

ps

Jitter, One Sigma

1

Tjis2

Fixed CLK; Load=20pF

-

1

3

%

Jitter, Absolute

1

Tjab2

Fixed CLK; Load=20pF

-5

2

5

%

Jitter, Cycle to Cycle

1

Tcc1

CPU Clocks, Load=20pF BSEL=1

-

250

ps

Jitter, Cycle to Cycle

1

Tcc2

CPU Clocks, Load=20pF BSEL=1

VDDL=2.5V

-

350

ps

Input Frequency

1

Fi

12.0

14.318

16.0

MHz

Ratio of nominal to output

frequency

Fout1

With input driven at 14.31818MHz to

20.0, 48.0MHz

-1

-0.1

+1

ppm

Logic Input Capacitance

1

CIN

Logic input pins

-

5

-

pF

Crystal Oscillator Capacitance

1, 2

CINX

X1, X2 pins

2

4

6

pF

Power-on Time

1

ton

From VDD=1.6V to 1st crossing of

66.6 MHz VDD supply ramp < 40ms

-2.5

4.5

ms

Clock Skew Window1

Tsk1

CPU to CPU or SDRAM;

Load=20pF; @1.4V

(Same VDD)

-

150

250

ps

Clock Skew Window

1

Tsk2

BUS to BUS, SDRAM to SDRAM;

Load=20pF; @1.4V

-

300

500

ps

Clock Skew Window

1

Tsk3

CPU to BUS; Load=20pF; @1.4V

(CPU is early)

1.6

2.1

4.6

ns

Clock Skew Window

1

Tsk4

CPUL to BUS, VDDL=2.5V

Vth=1.25, CPUL (BUS Vth=1.4V)

0.50

1.50

3.0

ns

Clock Skew Window

1

Tsk5

SDRAM, CPUH (@3.3V, Vth=1.4V)

to CPUL (@2.5V Vth=1.25V)

Load=20pF

(2.5V CPUL is late)

100

600

850

ps

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9148F-13 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9148F-PPP-LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS9148F-49 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| ICS9148F-49LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| ICS9148F-49LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9147F-12 | 制造商:ICS 制造商全称:ICS 功能描述:Pentium/ProTM System and Cyrix⑩ Clock Chip |

| ICS9147F-14 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUM/ProTM |

| ICS9147F-16 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator & Integrated Buffers for PENTIUMTM |

| ICS9147F-22 | 制造商:ICS 制造商全称:ICS 功能描述:Pentium/ProTM System and Cyrix™ Clock Chip |

| ICS9148-02 | 制造商:ICS 制造商全称:ICS 功能描述:Pentium/ProTM System Clock Chip |

发布紧急采购,3分钟左右您将得到回复。