- 您现在的位置:买卖IC网 > PDF目录79612 > ICS91857AGT (INTEGRATED DEVICE TECHNOLOGY INC) 91857 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF资料下载

参数资料

| 型号: | ICS91857AGT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 91857 SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封装: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-48 |

| 文件页数: | 1/16页 |

| 文件大小: | 164K |

| 代理商: | ICS91857AGT |

Integrated

Circuit

Systems, Inc.

ICS91857

0494C—08/15/05

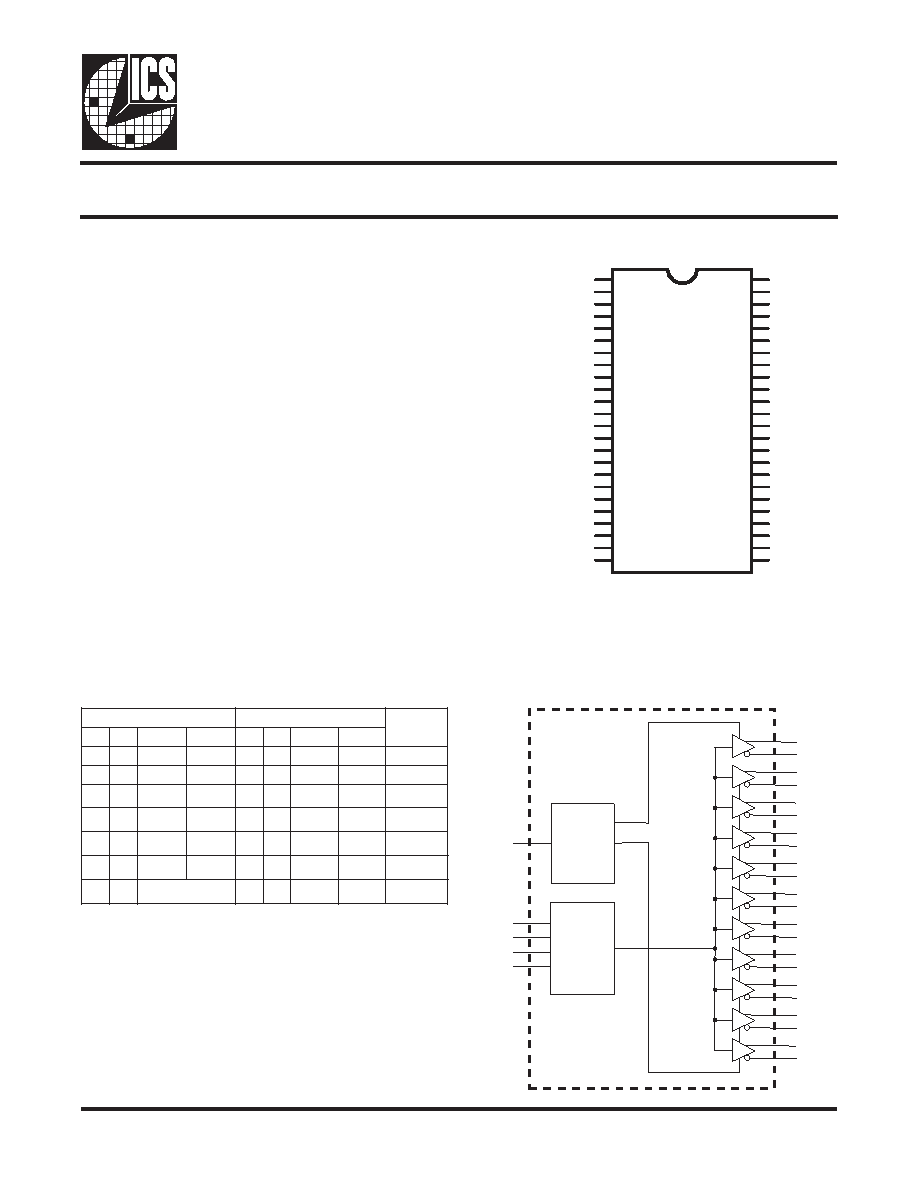

Block Diagram

Value SSTL_2 Clock Driver (60MHz - 220MHz)

Pin Configuration

48-Pin TSSOP

Recommended Application:

Zero delay board fan-out memory modules

Product Description/Features:

Meets PC3200 specification for DDRI-400 support

Low skew, low jitter PLL clock driver

1 to 10 differential clock distribution (SSTL_2)

Feedback pins for input to output synchronization

PD# for power management

Spread Spectrum tolerant inputs

Auto PD when input signal removed

Switching Characteristics:

CYCLE - CYCLE jitter (>100MHz):<75ps

OUTPUT - OUTPUT skew: <100ps

S

T

U

P

N

IS

T

U

P

T

U

O

e

t

a

t

S

L

P

D

V

A#

D

PT

N

I

_

K

L

CC

N

I

_

K

L

CT

K

L

CC

K

L

CT

T

U

O

_

B

FC

T

U

O

_

B

F

D

N

GH

L

H

L

H

L

H

f

o

/

d

e

s

a

p

y

B

D

N

GH

H

L

H

L

H

L

f

o

/

d

e

s

a

p

y

B

V

5

.

2

)

m

o

n

(

LL

H

Z

f

o

V

5

.

2

)

m

o

n

(

LH

LZ

Z

f

o

V

5

.

2

)

m

o

n

(

HL

H

L

H

n

o

V

5

.

2

)

m

o

n

(

HH

L

H

L

H

L

n

o

V

5

.

2

)

m

o

n

(

X)

z

H

M

0

2

<

)

1

(

ZZ

Z

f

o

Functionality

PLL

FB_INT

FB_INC

CLK_INC

CLK_INT

PD#

Control

Logic

FB_OUTT

FB_OUTC

CLKT0

CLKT1

CLKT2

CLKT3

CLKT4

CLKT5

CLKT6

CLKT7

CLKT8

CLKT9

CLKC0

CLKC1

CLKC2

CLKC3

CLKC4

CLKC5

CLKC6

CLKC7

CLKC8

CLKC9

6.10 mm. Body, 0.50 mm. pitch TSSOP

GND

CLKC0

CLKT0

VDD

CLKT1

CLKC1

GND

CLKC2

CLKT2

VDD

CLK_INT

CLK_INC

VDD

AVDD

AGND

GND

CLKC3

CLKT3

VDD

CLKT4

CLKC4

GND

CLKC5

CLKT5

VDD

CLKT6

CLKC6

GND

CLKC7

CLKT7

VDD

PD#

FB_INT

FB_INC

VDD

FB_OUTC

FB_OUTT

GND

CLKC8

CLKT8

VDD

CLKT9

CLKC9

GND

ICS91

8

57

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

相关PDF资料 |

PDF描述 |

|---|---|

| ICS95V857AL-T | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V857AHILF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA56 |

| ICS95V857ALILF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS97ULP877BK | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| ICS9112AM-27LF | 9112 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS91857YGLFT-LF-T | 制造商:ICS 制造商全称:ICS 功能描述:Value SSTL_2 Clock Driver (60MHz - 220MHz) |

| ICS91857YLLFT-LF-T | 制造商:ICS 制造商全称:ICS 功能描述:Value SSTL_2 Clock Driver (60MHz - 220MHz) |

| ICS9212-13 | 制造商:ICS 制造商全称:ICS 功能描述:Direct Rambus⑩ Clock Generator |

| ICS9212AF-13 | 功能描述:IC CLK GEN DIRECT RAMBUS 24-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS9212AF-13LF | 功能描述:IC CLK GEN DIRECT RAMBUS 24-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。