- 您现在的位置:买卖IC网 > PDF目录9600 > ICS932S200BGT (IDT, Integrated Device Technology Inc)IC FREQ TIMING GENERATOR 56TSSOP PDF资料下载

参数资料

| 型号: | ICS932S200BGT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 8/13页 |

| 文件大小: | 0K |

| 描述: | IC FREQ TIMING GENERATOR 56TSSOP |

| 标准包装: | 2,000 |

| 类型: | 时钟/频率发生器 |

| PLL: | 是 |

| 主要目的: | 服务器 |

| 输入: | 晶体 |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:20 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 133MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 56-TFSOP(0.240",6.10mm 宽) |

| 供应商设备封装: | 56-TSSOP |

| 包装: | 带卷 (TR) |

| 其它名称: | 932S200BGT |

4

ICS932S200

0427D—12/15/08

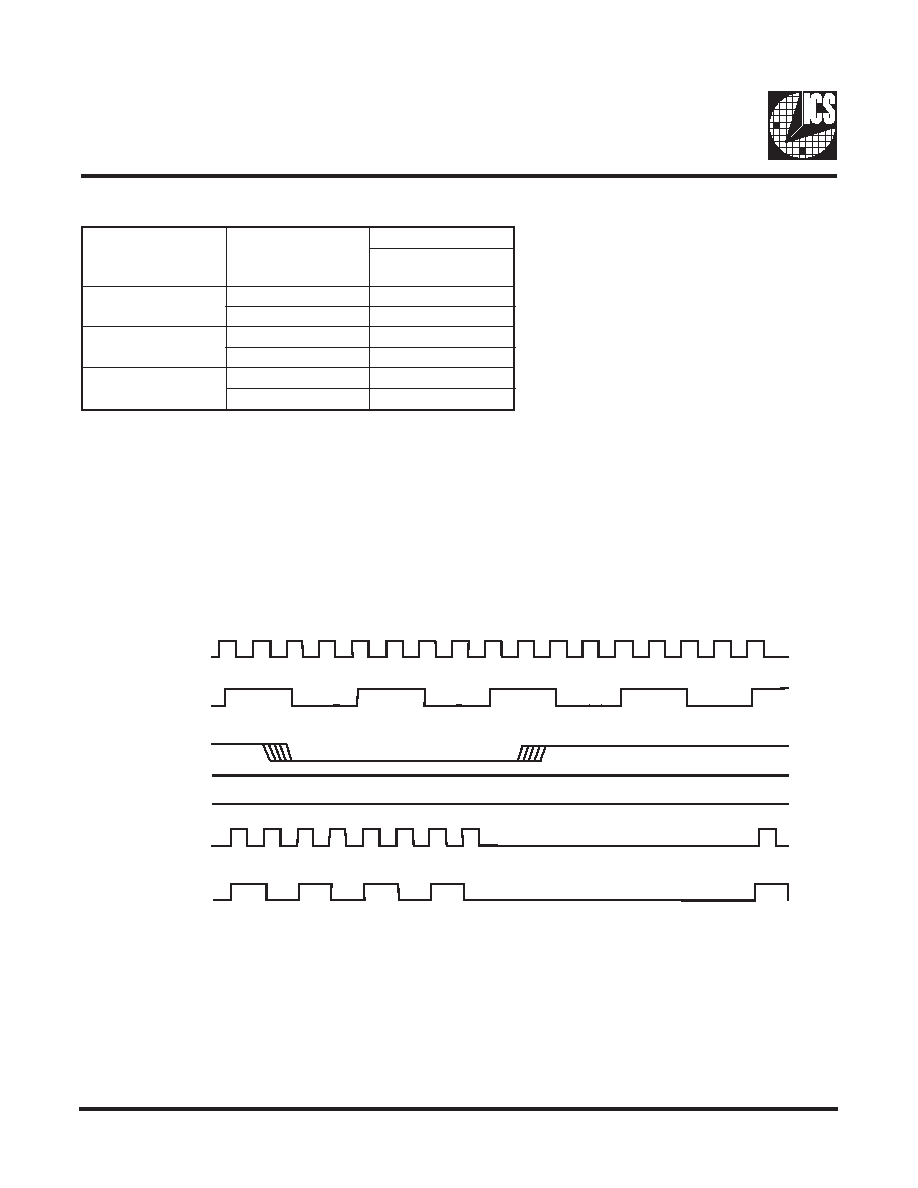

Power Management Requirements:

Note:

1. Clock on/off latency is defined in the number of rising edges of free running PCICLKs between the clock disable goes

low/high to the first valid clock comes out of the device.

2. Power up latency is when PWR_DWN# goes inactive (high to when the first valid clocks are dirven from the device.

l

a

g

n

i

Se

t

a

t

S

l

a

g

n

i

S

y

c

n

e

t

a

L

f

o

s

e

g

d

e

g

n

i

s

i

r

f

o

.

o

N

K

L

C

I

C

P

P

O

T

S

_

U

P

C

)

d

e

l

b

a

s

i

d

(

01

)

d

e

l

b

a

n

e

(

11

#

P

O

T

S

_

I

C

P

)

d

e

l

b

a

s

i

d

(

01

)

d

e

l

b

a

n

e

(

11

#

D

P

)

n

o

i

t

a

r

e

p

o

l

a

m

r

o

n

(

1S

m

3

)

n

w

o

d

r

e

w

o

p

(

0.

x

a

m

2

CPU_STOP# Timing Diagram

CPU_STOP# is an asynchronous input to the clock synthesizer. It is used to turn off the CPU and 3V66 clocks for

low power operation. CPU_STOP# is asserted asynchronously by the external clock control logic with the rising edge

of free running PCI clock (and hence CPU clock) and must be internally synchronized to the external output. All other

clocks will continue to run while the CPU clocks are disabled. The CPU clocks must always be stopped in a low state

and started in such a manner as to guarantee that the high pulse width is a full pulse.

Notes:

1. All timing is referenced to the internal CPUCLK.

2. The internal label means inside the chip and is a reference only.

This in fact may not be the way that the control is designed.

3. 3V66 clocks also stop/start before

4. PD# and PCI_STOP# are shown in a high state.

5. Diagrams shown with respect to 133MHz. Similar operation when

CPU is 100MHz

CPUCLK

(internal)

(externall)

PCICLK

PCI_STOP#

CPU_STOP#

PD#

CPUCLK

3V66

相关PDF资料 |

PDF描述 |

|---|---|

| VE-J1M-MW-B1 | CONVERTER MOD DC/DC 10V 100W |

| ICS932S203AFLNT | IC FREQ GEN W/CPU CLOCK 56-SSOP |

| ICL3245ECA-T | IC 3DRVR/5RCVR RS232 3V 28-SSOP |

| VE-BWZ-MV-F4 | CONVERTER MOD DC/DC 2V 60W |

| ICS932S203AFLFT | IC FREQ GEN W/CPU CLOCK 56-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS932S200YF-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for Dual Server/Workstation Systems |

| ICS932S200YG-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for Dual Server/Workstation Systems |

| ICS932S202 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for Differential PIIIType Dual-CPU Systems |

| ICS932S203 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Frequency Generator with 133MHz Differential CPU Clocks |

| ICS932S203AF | 制造商:INT_CIR_SYS 功能描述: |

发布紧急采购,3分钟左右您将得到回复。