- 您现在的位置:买卖IC网 > PDF目录362809 > ICS932S200YF-T Frequency Timing Generator for Dual Server/Workstation Systems PDF资料下载

参数资料

| 型号: | ICS932S200YF-T |

| 英文描述: | Frequency Timing Generator for Dual Server/Workstation Systems |

| 中文描述: | 频率为双服务器/工作站系统时序发生器 |

| 文件页数: | 1/12页 |

| 文件大小: | 107K |

| 代理商: | ICS932S200YF-T |

General Description

Features

Generates the following system clocks:

- 6 CPU clocks ( 2.5V, 100/133MHz)

- 6 PCI clocks, including 1 free running(3.3V,

33MHz)

- 3 IOAPIC clocks (2.5V, 16.67MHz)

- 2 Fixed frequency 66MHz clocks(3.3V, 66MHz)

- 2 REF clocks(3.3V, 14.318MHz)

- 1 USB clock (3.3V, 48MHz)

Efficient power management through PD#,

CPU_STOP# and PCI_STOP#.

0.5% typical down spread modulation on CPU, PCI,

IOAPIC and 3V66 output clocks.

Uses external 14.318MHz crystal.

ICS932S200

Integrated

Circuit

Systems, Inc.

0427C—07/03/02

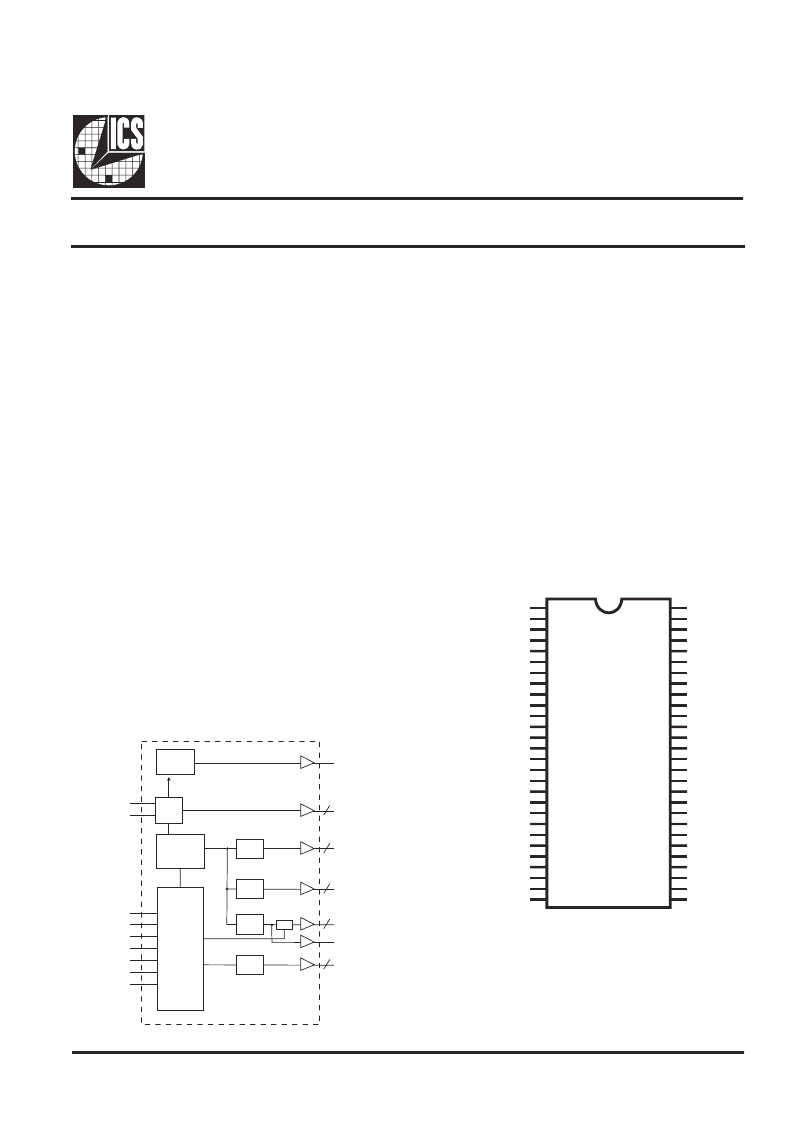

Block Diagram

Frequency Timing Generator for Dual Server/Workstation Systems

Pin Configuration

56-pin 300 mil SSOP

56-pin 240 mil TSSOP

The ICS932S200 is a dual CPU clock generator for

serverworks HE-T, HE-SL-T, LE-T chipsets for P III type

processors in a Dual-CPU system. Single ended CPU

clocks provide faster than 1.5V/ns transition times by

parallel connection of 2 CPU pins to each processor.

Spread Spectrum may be enabled by driving the

SPREAD# pin active. Spread spectrum typically

reduces system EMI by 8dB to 10dB. This simplifies

EMI qualification without resorting to board design

iterations or costly shielding. The

ICS932S200

employs

a proprietary closed loop design, which tightly controls

the percentage of spreading over process and

temperature variations.

Key Specification:

CPU Output Jitter: 150ps

IOAPIC Output Jitter: 250ps

3V66, PCI Output Jitter: 250ps

CPU Output Skew: <175ps

PCI Output Skew: <500ps

3V66 Output Skew <250ps

IOAPIC Output Skew <250ps

CPU to 3V66 Output Offset: 0 - 1.5ns (CPU leads)

CPU to PCI Output Offset: 1.5 - 4.0ns (CPU leads)

CPU to APIC Output Offset: 1.5 - 4.0ns (CPU

leads)

PCICLK_F

PLL2

PLL1

Spread

Spectrum

48MHz

CPUCLK (5:0)

IOAPIC (2:0)

3V66 (1:0)

PCICLK (4:0)

5

3

2

6

2

X1

X2

XTAL

OSC

CPU

DIVDER

IOAPIC

DIVDER

3V66

DIVDER

DIPCI

Stop

PD#

PCI_STOP#

CPU_STOP#

SPREAD#

SEL 133/100#

SEL0

SEL1

Control

Logic

Config.

Reg.

REF (1:0)

GND

REF0

REF1

VDD

X1

X2

GND

GND

PCICLK_F

VDD

PCICLK0

PCICLK1

GND

PCICLK2

PCICLK3

VDD

VDD

PCICLK4

GND

GND

GND

VDD

VDD

GND

3V66_0

3V66_1

VDD

SEL 133/100#

VDDL

IOAPIC2

IOAPIC1

IOAPIC0

GND

VDDL

CPUCLK5

CPUCLK4

GND

VDDL

CPUCLK3

CPUCLK2

GND

VDDL

CPUCLK1

CPUCLK0

GND

VDD

GND

PCI_STOP#

CPU_STOP#

PD#

SPREAD#

SEL1

SEL0

VDD

48MHz

GND

I

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

相关PDF资料 |

PDF描述 |

|---|---|

| ICS932S200YG-T | Frequency Timing Generator for Dual Server/Workstation Systems |

| ICS94241 | Programmable TCH⑩ for Differential PIII⑩ Processor |

| ICS94241FLF-T | Programmable TCH⑩ for Differential PIII⑩ Processor |

| ICS950218 | Programmable Timing Control Hub TM for P4 TM |

| ICS950218YFLF-T | Programmable Timing Control Hub TM for P4 TM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS932S200YG-T | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for Dual Server/Workstation Systems |

| ICS932S202 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Timing Generator for Differential PIIIType Dual-CPU Systems |

| ICS932S203 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Frequency Generator with 133MHz Differential CPU Clocks |

| ICS932S203AF | 制造商:INT_CIR_SYS 功能描述: |

| ICS932S203AFLF | 功能描述:IC FREQ GEN W/CPU CLOCK 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。