- 您现在的位置:买卖IC网 > PDF目录224008 > ICS93720YGLFT PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF资料下载

参数资料

| 型号: | ICS93720YGLFT |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封装: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-48 |

| 文件页数: | 1/8页 |

| 文件大小: | 291K |

| 代理商: | ICS93720YGLFT |

Integrated

Circuit

Systems, Inc.

ICS93720

Preliminary Product Preview

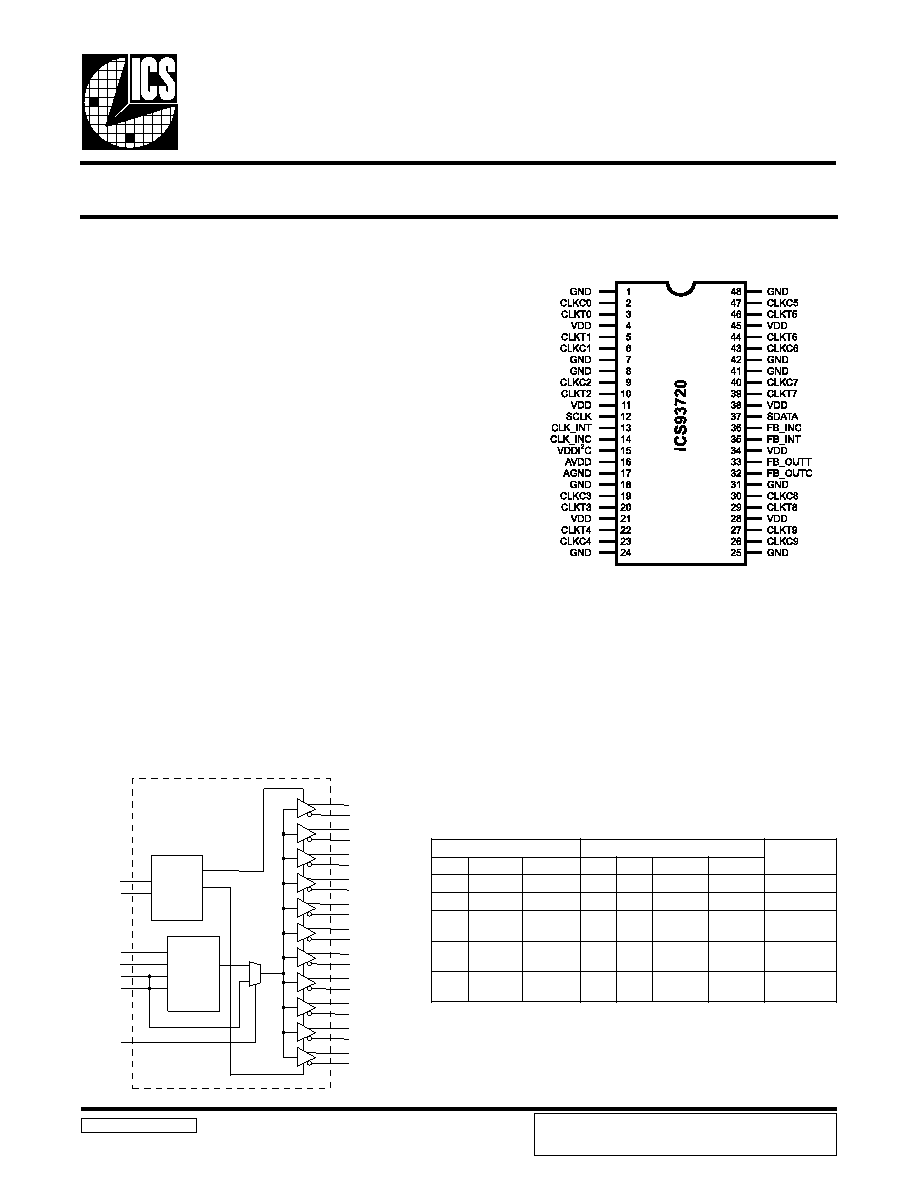

Block Diagram

DDR Phase Lock Loop Clock Driver

93720 Rev C 07/05/01

Pin Configuration

48-Pin TSSOP

RecommendedApplication:

DDR Clock Driver

Product Description/Features:

Low skew, low jitter PLL clock driver

I

2C for functional and output control

Feedback pins for input to output synchronization

Spread Spectrum tolerant inputs

Bypass mode mux

Switching Characteristics:

PEAK - PEAK jitter (66MHz): <120ps

PEAK - PEAK jitter (>100MHz): <75ps

CYCLE - CYCLE jitter (66MHz):<120ps

CYCLE - CYCLE jitter (>100MHz):<65ps

OUTPUT - OUTPUT skew: <100ps

Output Rise and Fall Time: 650ps - 950ps

DUTY CYCLE: 49.5% - 50.5%

PLL

FB_INT

FB_INC

CLK_INC

CLK_INT

SCLK

SDATA

Control

Logic

FB_OUTT

FB_OUTC

CLKT0

CLKT1

CLKT2

CLKT3

CLKT4

CLKT5

CLKT6

CLKT7

CLKT8

CLKT9

CLKC0

CLKC1

CLKC2

CLKC3

CLKC4

CLKC5

CLKC6

CLKC7

CLKC8

CLKC9

Control Bit

Functionality

S

T

U

P

N

IS

T

U

P

T

U

O

e

t

a

t

S

L

P

D

V

AT

N

I

_

K

L

CC

N

I

_

K

L

CT

K

L

CC

K

L

CT

T

U

O

_

B

FC

T

U

O

_

B

F

D

N

GL

H

L

H

L

H

f

O

/

d

e

s

a

p

y

B

D

N

GH

L

H

L

H

L

f

O

/

d

e

s

a

p

y

B

V

5

.

2

)

m

o

n

(

LH

L

H

L

H

n

O

V

5

.

2

)

m

o

n

(

HL

H

L

H

L

n

O

V

5

.

2

)

m

o

n

(

z

H

M

0

2

<z

H

M

0

2

<Z

-

i

HZ

-

i

HZ

-

i

HZ

-

i

Hf

f

O

PRODUCT PREVIEW documents contain information on new

products in the sampling or preproduction phase of development.

Characteristic data and other specifications are subject to change

without notice.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9DB104YGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ICS9FG108CG-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICSSSTUAF32868BHLFT | 32868 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA176 |

| IDT2309-1HDCGI8 | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| IDT54FCT373CTEB | FCT SERIES, 8-BIT DRIVER, TRUE OUTPUT, CDFP20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS93722 | 制造商:ICS 制造商全称:ICS 功能描述:Low Cost DDR Phase Lock Loop Zero Delay Buffer |

| ICS93722CFLF | 功能描述:IC DDR PLL ZD BUFFER 28-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS93722CFLFT | 功能描述:IC DDR PLL ZD BUFFER 28-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS93722YFLFT | 制造商:ICS 制造商全称:ICS 功能描述:Low Cost DDR Phase Lock Loop Zero Delay Buffer |

| ICS93725 | 制造商:ICS 制造商全称:ICS 功能描述:DDR and SDRAM Zero Delay Buffer |

发布紧急采购,3分钟左右您将得到回复。