- 您现在的位置:买卖IC网 > PDF目录79611 > ICS93732AFLF (INTEGRATED DEVICE TECHNOLOGY INC) 93732 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 6 INVERTED OUTPUT(S), PDSO28 PDF资料下载

参数资料

| 型号: | ICS93732AFLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 93732 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 6 INVERTED OUTPUT(S), PDSO28 |

| 封装: | 0.209 INCH, GREEN, MO-150, SSOP-28 |

| 文件页数: | 10/11页 |

| 文件大小: | 126K |

| 代理商: | ICS93732AFLF |

8

ICS93732

0578I—05/18/05

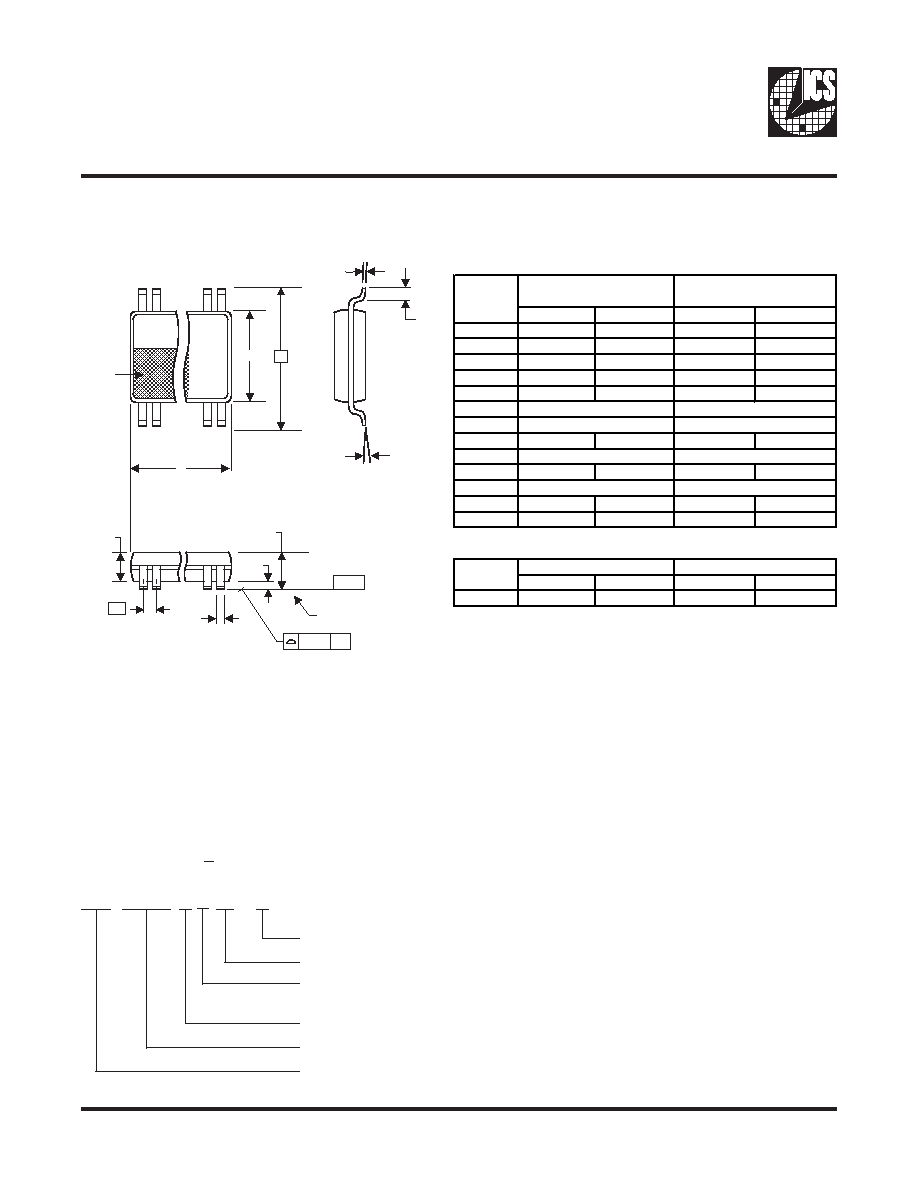

4.40 mm. Body, 0.65 mm. pitch TSSOP

(173 mil)

(0.0256 Inch)

INDEX

AREA

INDEX

AREA

12

1 2

N

D

E1

E

α

SEATING

PLANE

SEATING

PLANE

A1

A

A2

e

-C-

- C -

b

c

L

aaa C

Ordering Information

ICS93732yGLF -T

Designation for tape and reel packaging

RoHS Compliant

Package Type

G = TSSOP

Revision Designator (will not correlate with datasheet revision)

Device Type

Prefix

ICS = Standard Device

Example:

ICS XXXX y G LF - T

MIN

MAX

MIN

MAX

A

--

1.20

--

.047

A1

0.05

0.15

.002

.006

A2

0.80

1.05

.032

.041

b

0.19

0.30

.007

.012

c

0.09

0.20

.0035

.008

D

E

E1

4.30

4.50

.169

.177

e

L

0.45

0.75

.018

.030

N

α

0°

8°

0°

8°

aaa

--

0.10

--

.004

VARIATIONS

MIN

MAX

MIN

MAX

28

9.60

9.80

.378

.386

10-0035

SYMBOL

In Millimeters

In Inches

COMMON DIMENSIONS

SEE VARIATIONS

6.40 BASIC

0.252 BASIC

0.65 BASIC

0.0256 BASIC

SEE VARIATIONS

N

D mm.

D (inch)

Reference Doc.: JEDEC Publication 95, MO-153

相关PDF资料 |

PDF描述 |

|---|---|

| ICS93716AFLF | 93716 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ICS97U870AKI | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| ICS95VLP857AH-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA56 |

| ICS9214DGLF-T | 9214 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| ICS9214DGLF | 9214 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS93732AFLFT | 功能描述:IC DDR PLL ZD BUFFER 28-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS93732AFT | 功能描述:IC DDR PLL ZD BUFFER 28-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS93732FLF-T | 制造商:ICS 制造商全称:ICS 功能描述:Low Cost DDR Phase Lock Loop Zero Delay Buffer |

| ICS93732G-T | 制造商:ICS 制造商全称:ICS 功能描述:Low Cost DDR Phase Lock Loop Zero Delay Buffer |

| ICS93735 | 制造商:ICS 制造商全称:ICS 功能描述:DDR Phase Lock Loop Zero Delay Clock Buffer |

发布紧急采购,3分钟左右您将得到回复。