- 您现在的位置:买卖IC网 > PDF目录65535 > ICS93V857YGT (INTEGRATED DEVICE TECHNOLOGY INC) PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF资料下载

参数资料

| 型号: | ICS93V857YGT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封装: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-48 |

| 文件页数: | 1/9页 |

| 文件大小: | 323K |

| 代理商: | ICS93V857YGT |

Integrated

Circuit

Systems, Inc.

ICS93V857

Preliminary Product Preview

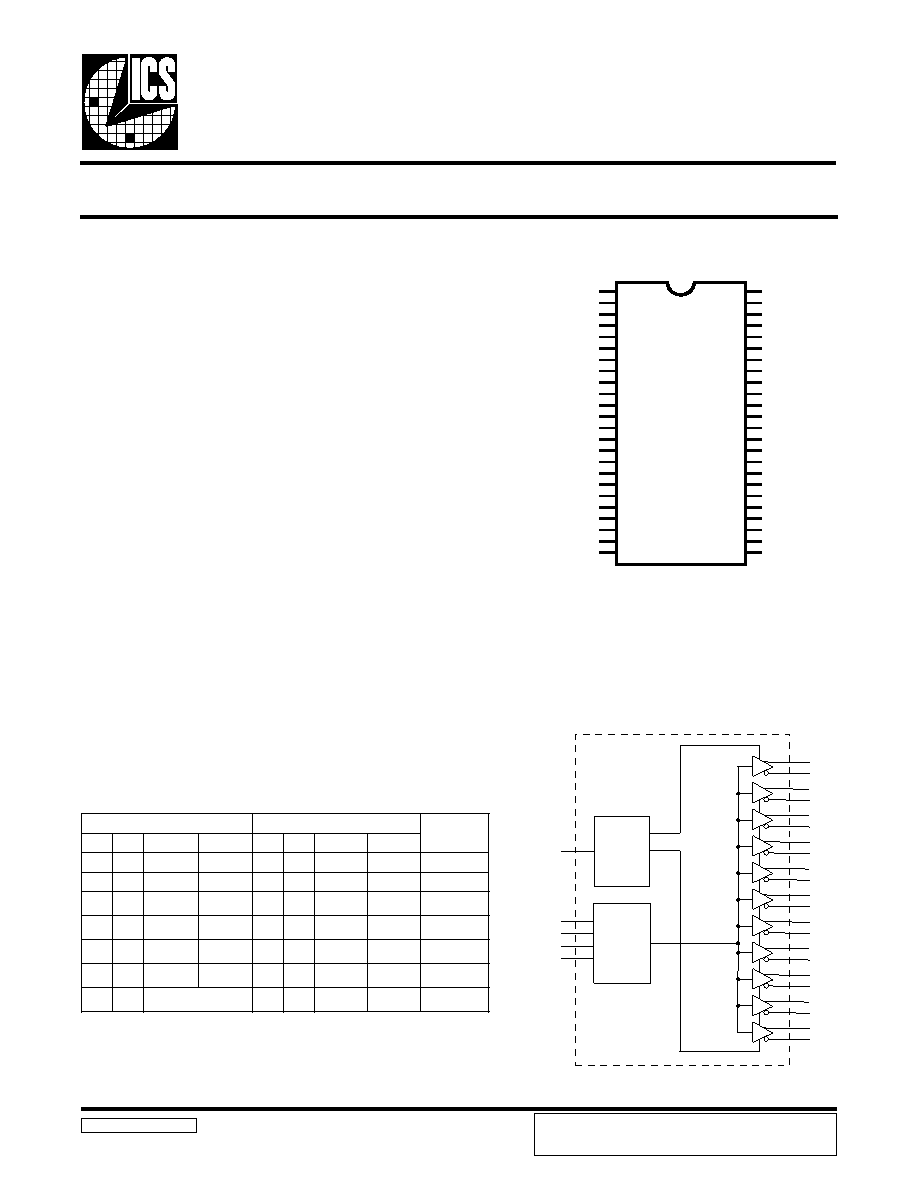

Block Diagram

DDR Phase Lock Loop Clock Driver

93V857 Rev A 11/10/00

Pin Configuration

48-Pin TSSOP

RecommendedApplication:

DDR Memory Modules

Product Description/Features:

Low skew, low jitter PLLclock driver

1 to 10 differential clock distribution

Feedback pins for input to output synchronization

PD# for power management

Spread Spectrum tolerant inputs

Specifications:

Meet JEDEC standard #82 for registered DDR

clock driver.

Switching Characteristics:

PEAK - PEAK jitter (66MHz): <120ps

PEAK - PEAK jitter (>100MHz): <75ps

CYCLE-CYCLEjitter(66MHz):<120ps

CYCLE-CYCLEjitter(>100MHz):<65ps

OUTPUT - OUTPUT skew: <100ps

Output Rise and Fall Time: 650ps - 950ps

DUTYCYCLE:49.5%-50.5%

GND

CLKC0

CLKT0

VDD

CLKT1

CLKC1

GND

CLKC2

CLKT2

VDD

CLK_INT

CLK_INC

VDD

AVDD

AGND

GND

CLKC3

CLKT3

VDD

CLKT4

CLKC4

GND

CLKC5

CLKT5

VDD

CLKT6

CLKC6

GND

CLKC7

CLKT7

VDD

PD#

FB_INT

FB_INC

VDD

FB_OUTC

FB_OUTT

GND

CLKC8

CLKT8

VDD

CLKT9

CLKC9

GND

ICS93V857

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

S

T

U

P

N

IS

T

U

P

T

U

O

e

t

a

t

S

L

P

D

V

A#

D

PT

N

I

_

K

L

CC

N

I

_

K

L

CT

K

L

CC

K

L

CT

T

U

O

_

B

FC

T

U

O

_

B

F

D

N

GH

L

H

L

H

L

H

f

o

/

d

e

s

a

p

y

B

D

N

GH

H

L

H

L

H

L

f

o

/

d

e

s

a

p

y

B

V

5

.

2

)

m

o

n

(

LL

H

Z

f

o

V

5

.

2

)

m

o

n

(

LH

L

Z

f

o

V

5

.

2

)

m

o

n

(

HL

H

L

H

n

o

V

5

.

2

)

m

o

n

(

HH

L

H

L

H

L

n

o

V

5

.

2

)

m

o

n

(

X)

z

H

M

0

2

<

)

1

(

ZZ

Z

f

o

Functionality

PLL

FB_INT

FB_INC

CLK_INC

CLK_INT

PD#

Control

Logic

FB_OUTT

FB_OUTC

CLKT0

CLKT1

CLKT2

CLKT3

CLKT4

CLKT5

CLKT6

CLKT7

CLKT8

CLKT9

CLKC0

CLKC1

CLKC2

CLKC3

CLKC4

CLKC5

CLKC6

CLKC7

CLKC8

CLKC9

PRODUCT PREVIEW documents contain information on new

products in the sampling or preproduction phase of development.

Characteristic data and other specifications are subject to change

without notice.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS93V857YL-25LFT | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS93V857YG-25LFT | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS951601YFLF | 66.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS95V157YGLF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| ICS95V157YG-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS93V857YL-025T | 制造商:ICS 制造商全称:ICS 功能描述:2.5V Wide Range Frequency Clock Driver |

| ICS93V857YL-125T | 制造商:ICS 制造商全称:ICS 功能描述:2.5V Wide Range Frequency Clock Driver |

| ICS93V857YL-130T | 制造商:ICS 制造商全称:ICS 功能描述:2.5V Wide Range Frequency Clock Driver |

| ICS94201 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable System Frequency Generator for PII/III⑩ |

| ICS94201DF | 功能描述:IC FREQ GENERATOR PROGR 56-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。