- 您现在的位置:买卖IC网 > PDF目录67707 > ICS950812YFT 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | ICS950812YFT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 0.300 INCH, MO-118, SSOP-56 |

| 文件页数: | 19/29页 |

| 文件大小: | 253K |

| 代理商: | ICS950812YFT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

26

ICS950812

0542H—04/08/05

PD# Functionality

#

D

PT

K

L

C

U

P

CC

K

L

C

U

P

C6

6

V

3T

U

O

_

z

H

M

6

F

_

K

L

C

I

C

P

K

L

C

I

C

P

K

L

C

I

C

P

T

O

D

/

B

S

U

z

H

M

8

4

1l

a

m

r

o

Nl

a

m

r

o

Nz

H

M

6

6N

I

_

z

H

M

6

2

/

N

I

_

z

H

M

6

62

/

N

I

_

z

H

M

6

z

H

M

8

4

0t

l

u

M

*

f

e

r

it

a

o

l

Fw

o

Lw

o

Lw

o

Lw

o

Lw

o

L

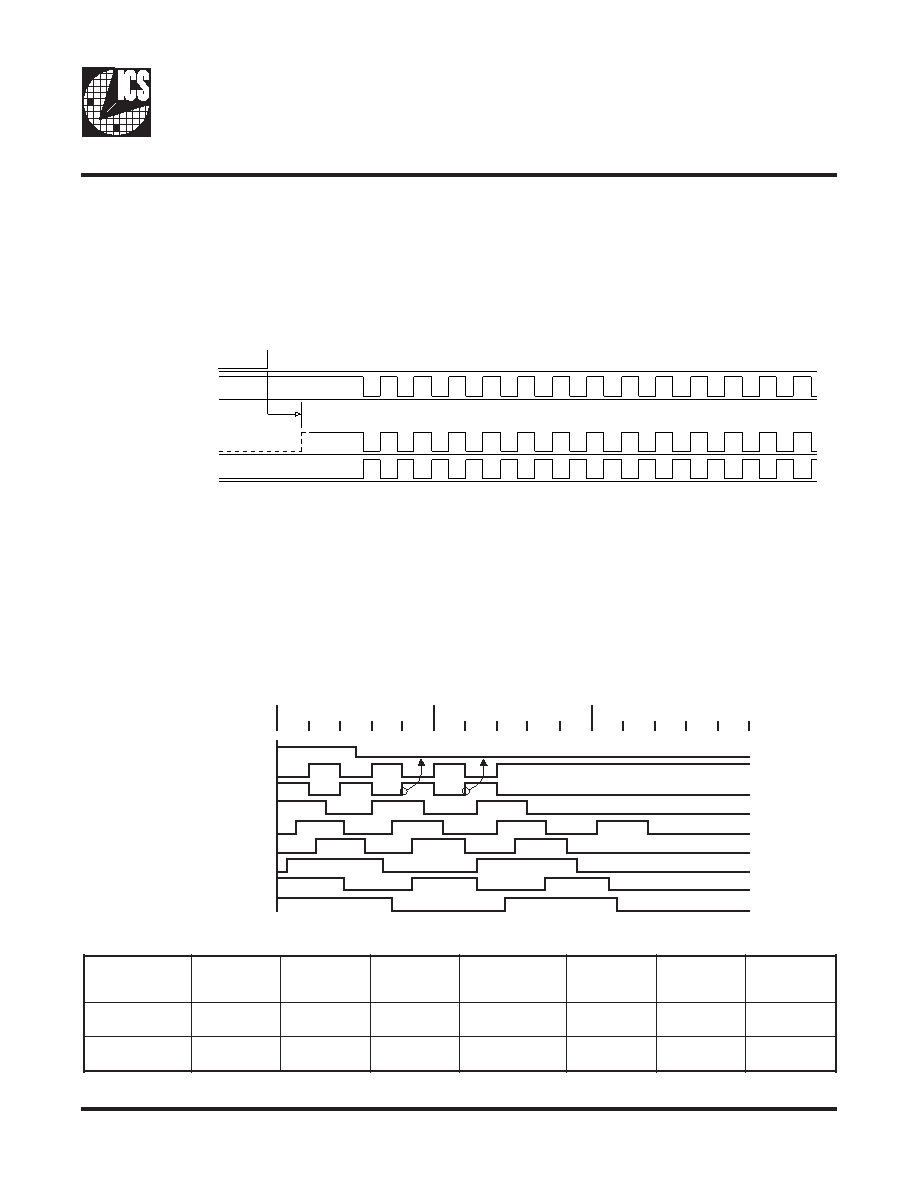

CPU_STOP# - De-assertion (transition from logic "0" to logic "1")

De-assertion of CPU_STOP# Waveforms

All CPU outputs that were stopped are to resume normal operation in a glitch free manner. The maximum latency from the

de-assertion to active outputs is to be defined to be between 2 - 6 CPU clock periods (2 clocks are shown). If the I2C

Bit 6 of Byte 1 is programmed to "1" then the stopped CPU outputs will be driven High within 10 nS of CPU_Stop# de-

assertion.

When PWRDWN# is sampled low by two consecutive rising edges of CPU clock, then all clock outputs except CPU clocks

must be held low on their next high to low transitions. When the I2C Bit 6 of Byte 0 is programmed to '0' CPU clocks must

be held with the CPU clock pin driven high with a value of 2 x Iref, and CPU# undriven. If Bit 6 of Byte 0 is '1' then both

CPU and CPU# are undriven. Note the example below shows CPU = 133 MHz and Bit 6 of Byte 0 = '0', this diagram and

description is applicable for all valid CPU frequencies 66, 100, 133, 200 MHz.

Due to the state if the internal logic, stopping and holding the REF clock outputs in the LOW state may require more than

one clock cycle to complete.

PD# - Assertion (transition from logic "1" to logic "0")

Power Down Assertion of Waveforms

0ns

PD#

CPUCLKT 100MHz

CPUCLKC 100MHz

3V66MHz

66MHz_IN

66MHz_OUT

PCICLK 33MHz

USB 48MHz

REF 14.318MHz

25ns

50ns

CPU_STOP#

CPUCLKT(2:0)

*CPUCLKT(2:0)TS

CPUCLKC(2:0)

Tdrive_CPU_STOP# <10ns @ 200mV

*Signal TS is CPUCLKT in Tri-State mode

相关PDF资料 |

PDF描述 |

|---|---|

| ICS950813YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950902YFLF-T | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950902YGLF-T | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950902YGT | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950908YG-T | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS950812YGLFT | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950813 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950813YFT | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950813YGT | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950818 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

发布紧急采购,3分钟左右您将得到回复。