- 您现在的位置:买卖IC网 > PDF目录67707 > ICS950812YFT 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | ICS950812YFT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 0.300 INCH, MO-118, SSOP-56 |

| 文件页数: | 23/29页 |

| 文件大小: | 253K |

| 代理商: | ICS950812YFT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页

3

ICS950812

0542H—04/08/05

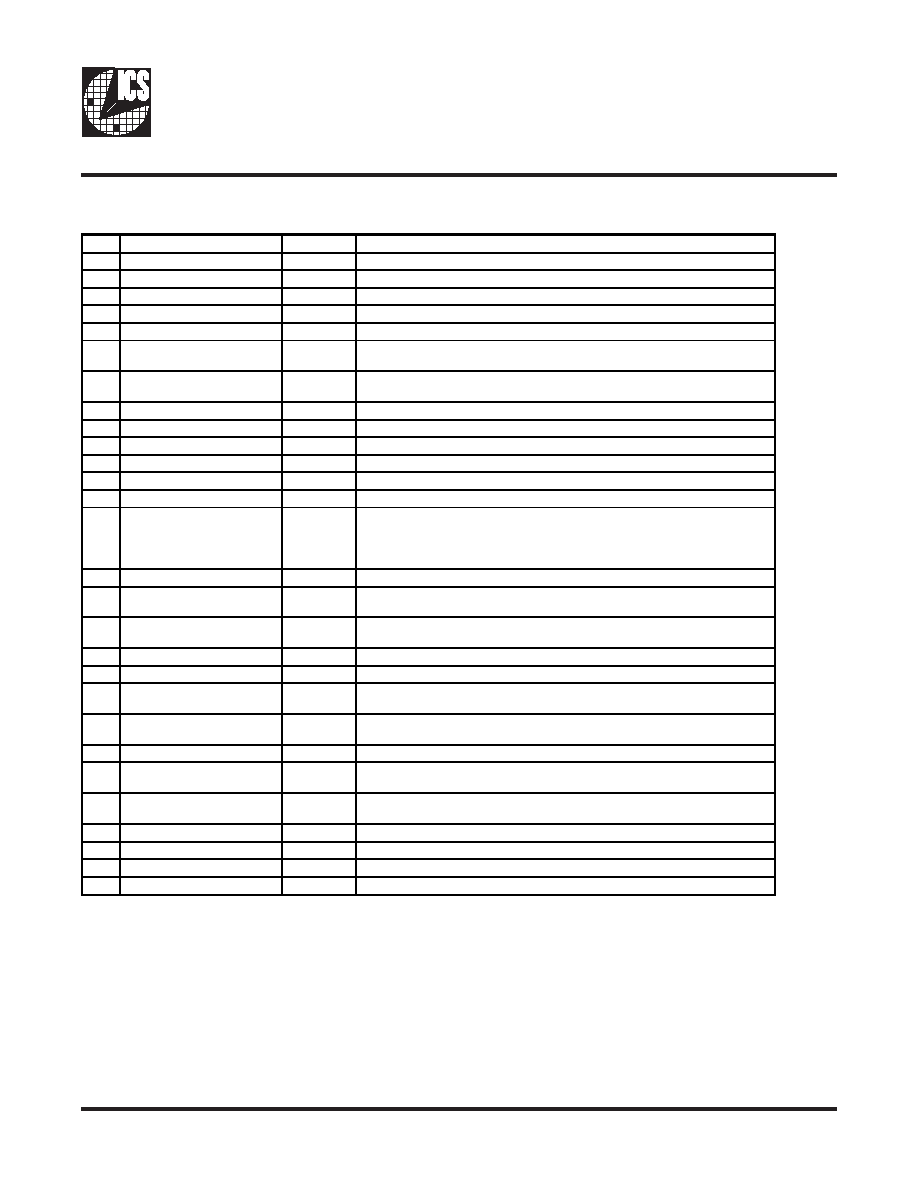

Pin Configuration (Continued)

PIN # PIN NAME

PIN TYPE

DESCRIPTION

29

SDATA

I/O

Data pin for I2C circuitry 5V tolerant

30

SCLK

IN

Clock pin of I2C circuitry 5V tolerant

31

GND

PWR

Ground pin.

32

VDD3V66

PWR

Power pin for the 3V66 clocks.

33

3V66_0/FS5**

I/O

Frequency select latch input pin / 3.3V 66.66MHz clock output.

34

PCI_STOP#*

IN

Stops all PCICLKs besides the PCICLK_F clocks at logic 0 level, when input

low

35

3V66_1/VCH_CLK/FS4**

I/O

Frequency select latch input pin / 3.3V 66.66MHz clock output / 48MHz

VCH clock output.

36

GND

PWR

Ground pin.

37

VDD48

PWR

Power pin for the 48MHz output.3.3V

38

48MHz_DOT

OUT

48MHz clock output.

39

48MHz_USB/FS3**

I/O

Frequency select latch input pin / 3.3V 48MHz clock output.

40

FS2

IN

Frequency select pin.

41

GND

PWR

Ground pin.

42

IREF

OUT

This pin establishes the reference current for the differential current-mode

output pairs. This pin requires a fixed precision resistor tied to ground in

order to establish the appropriate current. 475 ohms is the standard value.

43

MULTSEL*

IN

3.3V LVTTL input for selection the current multiplier for CPU outputs

44

CPUCLKC2

OUT

Complimentary clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

45

CPUCLKT2

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

46

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

47

GND

PWR

Ground pin.

48

CPUCLKC1

OUT

Complimentary clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

49

CPUCLKT1

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

50

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

51

CPUCLKC0

OUT

Complimentary clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

52

CPUCLKT0

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

53

CPU_STOP#*

IN

Stops all CPUCLK besides the free running clocks

54

FS0

IN

Frequency select pin.

55

FS1

IN

Frequency select pin.

56

REF

OUT

14.318 MHz reference clock.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS950813YFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950902YFLF-T | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950902YGLF-T | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950902YGT | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950908YG-T | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS950812YGLFT | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950813 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950813YFT | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950813YGT | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| ICS950818 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

发布紧急采购,3分钟左右您将得到回复。