- 您现在的位置:买卖IC网 > PDF目录378603 > ICS951AI147L (Integrated Device Technology, Inc.) LOW SKEW, 1-TO-9 DIFFERENTIAL-TOLVCMOS ZERO DELAY BUFFER PDF资料下载

参数资料

| 型号: | ICS951AI147L |

| 厂商: | Integrated Device Technology, Inc. |

| 英文描述: | LOW SKEW, 1-TO-9 DIFFERENTIAL-TOLVCMOS ZERO DELAY BUFFER |

| 中文描述: | 低偏移,1到9微分TOLVCMOS零延迟缓冲器 |

| 文件页数: | 10/15页 |

| 文件大小: | 598K |

| 代理商: | ICS951AI147L |

IDT

/ ICS

DIFFERENTIAL-TO-LVCMOS ZERO DELAY BUFFER

10

ICS87951I-147 REV A JUNE 21, 2006

ICS87951I-147

LOW SKEW, 1-TO-9, DIFFERENTIAL-TO-LVCMOS ZERO DELAY BUFFER

F

IGURE

3C. H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

3.3V LVPECL D

RIVER

F

IGURE

3B. H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

3.3V LVPECL D

RIVER

F

IGURE

3D. H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

3.3V LVDS D

RIVER

3.3V

R1

50

R3

50

Zo = 50 Ohm

LVPECL

Zo = 50 Ohm

HiPerClockS

Input

CLK

nCLK

3.3V

R2

50

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

3.3V

R3

R2

84

Zo = 50 Ohm

3.3V

R4

LVPECL

R1

84

3.3V

D

IFFERENTIAL

C

LOCK

I

NPUT

I

NTERFACE

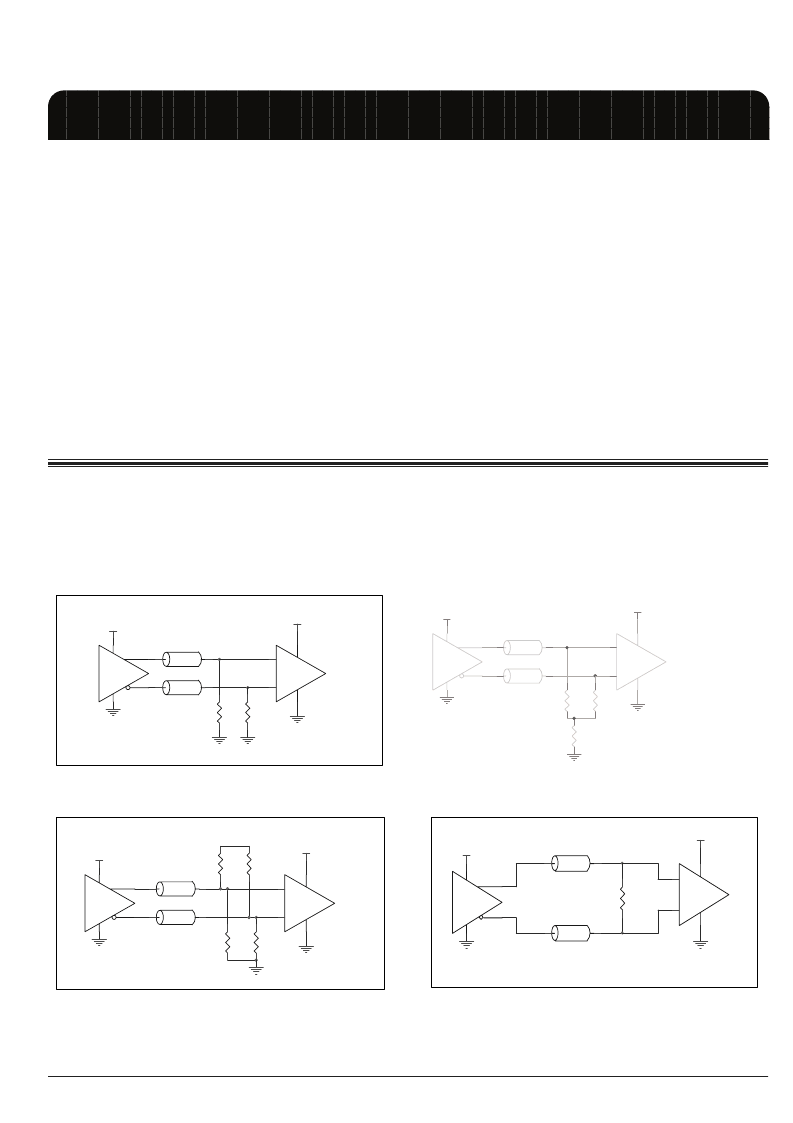

The CLK /nCLK accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL

and other differential signals. Both V

and V

must meet the

V

and V

input requirements. Figures 3A to 3D show interface

examples for the HiPerClockS CLK/nCLK input driven by the most

common driver types. The input interfaces suggested here are

F

IGURE

3A. H

I

P

ER

C

LOCK

S CLK/nCLK I

NPUT

D

RIVEN

BY

ICS H

I

P

ER

C

LOCK

S LVHSTL D

RIVER

examples only. Please consult with the vendor of the driver

component to confirm the driver termination requirements. For

example in Figure 3A, the input termination applies for ICS

HiPerClockS LVHSTL drivers. If you are using an LVHSTL driver

from another vendor, use their termination recommendation.

1.8V

R2

50

LVHSTL Driver

ICS

HiPerClockS

R1

50

LVHSTL

3.3V

Zo = 50 Ohm

Zo = 50 Ohm

HiPerClockS

CLK

nCLK

Zo = 50 Ohm

R1

100

3.3V

LVDS_Driver

Zo = 50 Ohm

Receiver

CLK

nCLK

3.3V

I

NPUTS

:

CLK I

NPUT

:

For applications not requiring the use of a clock input, it can be

left floating. Though not required, but for additional protection, a

1k

resistor can be tied from the CLK input to ground.

CLK/nCLK I

NPUT

:

For applications not requiring the use of the differential input,

both CLK and nCLK can be left floating. Though not required, but

for additional protection, a 1k

resistor can be tied from CLK to

ground.

LVCMOS C

ONTROL

P

INS

:

All control pins have internal pull-ups or pull-downs; additional

resistance is not required but can be added for additional

protection. A 1k

resistor can be used.

R

ECOMMENDATIONS

FOR

U

NUSED

I

NPUT

AND

O

UTPUT

P

INS

O

UTPUTS

:

LVCMOS O

UTPUT

:

All unused LVCMOS output can be left floating. There should be

no trace attached.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS889832 | LOW SKEW, 1-TO-4 DIFFERENTIAL-TOLVDS FANOUT BUFFER |

| ICS889832AK | LOW SKEW, 1-TO-4 DIFFERENTIAL-TOLVDS FANOUT BUFFER |

| ICS889832AKT | LOW SKEW, 1-TO-4 DIFFERENTIAL-TOLVDS FANOUT BUFFER |

| ICS889872 | DIFFERENTIAL-TO-LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION |

| ICS889872AK | DIFFERENTIAL-TO-LVDS BUFFER/DIVIDER W/INTERNAL TERMINATION |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS952001 | 制造商:ICS 制造商全称:ICS 功能描述:Preliminary Product Previes |

| ICS952001AF | 功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS952001AFLF | 功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS952001AFLFT | 功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS952001AFT | 功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。